MIPS32 M4K处理器内核SRAM接口应用

微控制器环境要求在尽可能小的封装里实现最多的通用I/O。存微控制器尺寸和成本的限制下,M4K内核内部不支持指令高速缓存(I-cache)或数据高速缓存(D-cache)的标准功能。但MIPS32 M4K内核所具有的一些特点使其非常适用于微控制器应用领域。这就涉及到本文重点讨论的一个内容--SRAM接口,这是MIPS32 M4K内核的一个标准功能。

微控制器应用需要仅用最少的接口逻辑就可以在处理器内核和存储系统之间实现紧密耦合。MIPS32M4K内核SRAM接口就是一个比较完美的解决方案。

M4K内核SRAM接口基本描述

M4K内核SRAM接口是M4K内核的通用高速存储器接口。它可为指令存储器和数据存储器路径提供低延迟接口,支持单周期和多周期存储器存取。 必须指出,SRAM接口不能直接与外部存储器件连接,若要实现外部存储连接,需使用一个外部存储控制器。必须使用固定映射表(FMT)和SRAM接口,以提供完整的存储器控制逻辑。

双模操作

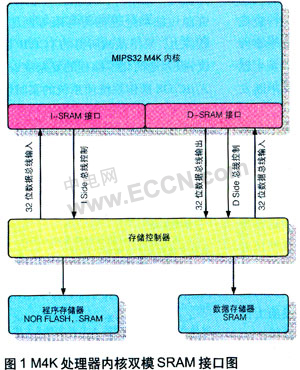

SRAM接口的初始配置称为双模。在这种模式下,指令和数据通道彼此隔离。数据有独立的读写总线(D-SRAM),还有D-SRAM接口控制信号和一个独立的指令侧(I-SRAM)接口,以及其互补I-SRAM控制信号。

I-SRAM接口具有改变信号输入方向的能力,需要时,可将D-SRAM读周期改变到I侧方向。这有助于改良的Harvard架构的实现,和非易失性数据在程序存储器中的存储。

双模有助于I-SRAM和D-SRAM接口的同步处理,消除任何可能出现在公用总线接口上的延迟,防止其减缓程序的执行。在这个模式下,内核可达到1.5 DMIPS/MHz的标称性能。双模结构如图1所示。

标准模式

标准模式是标准接口的一个配置选项,在这种模式下,为了节省必须从内核发送的信号总数,I-SRAM和D-SRAM信号合并在一起。除了数据写总线外,D-SRAM接口是完全禁用的,所有数据读周期都自动改变方向,以使用I-SRAM读总线。

在该模式中,内核的平均性能大概是1.2 DMIPS/MHz。然而,由SRAM接口内核暴露的活跃信号总数是122个,比双模节省87个信号。减少接口使用的活跃信号数量,对于成本非常有限、总裸片面积比绝对性能更重要的设计来说,是一种更经济有效的方式。

SRAM接口标准模式如图2所示。

处理中断

SRAM接口提供了中止指令处理的能力,这种能力可中止M4K内核5段流水线中任何指令处理。这有助于外部系统控制器立即响应外部事件,如中断请求或通过EJTAG调试接口请求。在处理典型微控制器应用中高度确定性性质时,快速响应外部中断事件至关重要。

对接口信号连接有限的器件提供支持

M4K处理器内核可通过特定字节通道,对接口信号连接有限的存储器件接口的能力进行控制,可帮助M4K内核以连续字节读取汇编32位字,然后在SRAM接口中进行内部汇编。

这个功能通常用于接口外设的总线锁存和总线停止的组合,如ADC。该类型的混合信号器件通常不提供32位位宽的接口。

总线锁存和总线停止

SRAM接口提供输入控制信号,在外部存储控制器禁用这个信号之前锁住数据总线,以防止CPU进一步写处理。由此,可不用担心多线程存储周期的损害。SRAM接口还提供控制信号,利于总线停止,使设计师将速度更慢的存储器和外设连接到系统成为可能。这些器件可包括速度更慢的非易失性RAM和混合信号器件,在将请求的数据传送到总线之前,它们需要更多的等待时间。

缓存关联信号

虽然M4K内核不包含任何高速缓存,但仍能指明出现在地址总线上的当前存储器地址是否可以进行缓存。外部存储控制器能够利用这些状态信号实现L2高速缓存结构。

M4K SRAM接口在微控制器领域的应用

利用上述这些功能,设计师们能够对于微控制器系统环境中使用M4K SRAM接口的多种优势有所认识。

首先,紧密耦合的接口意味着大多数处理任务是在单时钟周期内完成的。除非当设计师执行总线停止时,需要考虑速度较慢的存储器件的完成周期。而且,连接到该接口的控制逻辑必须只能处理指令和数据,以使整个逻辑设计不那么复杂。另外,可能还要锁住总线,使原子处理的完成能够不受排队周期的影响。

固定映射表(FMT)可减少外部存储控制器所需的逻辑和解码量。除了存储器映像外设,以及对微控制器可用的存储器件绝对尺寸外,有源区都在定义的边界之内。

在双模操作下,指令提取路径和数据读/写路径是独立的。这些独立的数据通道有助于存储控制器逻辑优化存储器件的类型和尺寸。

中止流水线中,任何处理的能力都有助于在调试环境中实现快速响应和精确的断点控制。

基本上,L2缓存可以使用M4K内核的本地信号执行,从而简化L2缓存控制器。

MIPS32M4K内核SRAM接口为M4K内核提供了一种高速、

- 智能铅酸蓄电池充电器的设计(01-02)

- 用微控制器或 DSP 电路控制开机/关机功能(06-22)

- 微控制器的市场前景及发展趋势(06-21)

- 基于AT89S52汉字多方式显示屏的设计(01-06)

- 灵活高效的数字解决方案满足新兴电源管理需求(01-10)

- 基于ARM微处理器的十回路智能配电监控单元的设计(11-17)