锁相环频率合成器的方案研究

随着大规模集成电路的发展,各种新型的频率合成器和频率合成方案不断涌现,利用锁相环频率合成技术研制出了很多频率合成集成电路。本文介绍一种以摩托罗拉公司生产的MC145152芯片的为基础的频率合成器。这种锁相环频率合成器的稳定度和准确度与基准频率一致,从总体结构上看由单片机、锁相环及可编程分频器三部分组成。其中可编程分频器是单片微机与锁相环之间的接口,同时也是组成数字锁相频率合成器的关键部件,在移动通信陆地电台等领域有着广泛的应用。

1 MC145152芯片的特点及功能

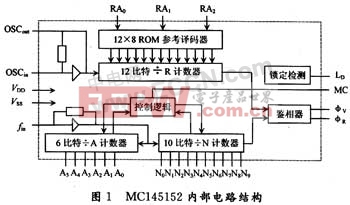

MC145152是MOTOROLA公司生产的大规模集成电路,是16比特并行输入并行输入数据编程的双模锁相环频率合成器,该芯片内含参考频率振荡器、可供用户选择的参考分频器(分频比为8,64,128,256,512,1 024,1 160,2 048),双端输出的数字鉴相器、控制逻辑、10比特可编程的÷N计数器(分频比为3~1 023)、6比特可编程÷A计数器(计数范围为0~63)和锁定检测等部分。其中,10比特÷N计数器、6比特÷A计数器、模拟控制逻辑和外接双模前置分频器组成吞脉冲程序分频器,吞脉冲程序分频器的总分频比为:N总=NP+A,其内部组成框图如图1所示。

|

(1)他与双模(P/(P+1))分频器同时使用,有一路双模分频控制输出MC。当MC为低电平时,双模分频器用(P+1)去除;当MC为高电平时,双模分频器用模数P去除。

(2)他有A计数器和N计数器两个计数器。他们与双模(P/(P+1))分频器提供了总分频值(NP+A)。其中,A、N计数器可预置。N的取值范围为3~1 023,A的取值范围为0~63。A计数器计数期间,MC为低电平;N计数器计数(N-A)期间,MC为高电平。

(3)他有一个参考振荡器,可外接晶体振荡器。

(4)他有一个R计数器,用来给参考振荡器分频,R计数器可预置,R的取值范围:8,64,128,256,512,1 024,1 160,2 048。

(5)他有两路鉴相信号输出,其中,φR,φV用来输出鉴相误差信号,LD用来输出相位锁定信号。

MC145152的工作原理;参考振荡器信号经R分频器分频后形成fR信号。压控振荡器信号经双模(P/(P+1))分频器分频,再经A,N计数器分频器后形成fv信号,fv=fvco/(NP+A)。fR信号和fV信号在鉴相器中鉴相,输出的误差信号(φR,φV)经低通滤波器形成直流信号,直流信号再去控制压控振荡器的频率。

当整个环路锁定后,fO=fR且同相,fVCO=(NP+A)fR,便可产生和基准频率同样稳定度和准确度的任意频率。

2 909~915 MHz数字锁相环频率合成器的设计

|

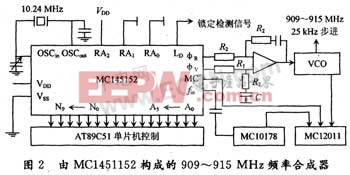

图2为移动通信909~915 MHz频率合成器的设计电路,其中压控振荡器输出的频率通过双模预分频器MC12054A预分频,再输出到可编程并行输入锁相环MC145152中,单片机AT89C51通过I/O口对MC145152进行编程,以改变其计数器的计数初值,从而改变分频比,鉴相器双输出端输出的误差信号φV和φR输入到双端输入的有源低通滤波器,输出信号直接对压控振荡器进行控制,构成了一个完整的数控锁相环。单片机接收人工调整、设置的数值,并对MC145152的计数器计数初值进行不同的预置,以锁定不同的频率,达到改变不同频点信号的目的。

2.1 909~915 MHz频率合成器元件的选取锁相环频率合成器选用芯片MC145152。晶振选用12.8 MHz的温补晶体,他的频率稳定度较高,可达10-8。低通滤波器选用运放芯片MC33171;双模分频器选用MC12011与MC10154串联组成÷64/65双模前置分频器,环路总分频比N总=N×64+A=36 360~36 600,N=568~571,A=0~63。

2.2 909~915 MHz频率合成器电路的设计

(1)MC145152芯片参数的设计

909~915 MHz频率合成器电路图如图2所示。

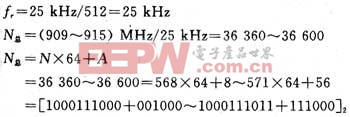

fVCO=909~915 MHz,P=64,晶体振荡器的频率为12.8 MHz,参考分频器R取512,RA2~RA0为100,则:

因此,N的取值范围为568~571,A的取值范围为0~63,对应分频比36 360,N计数器二进制为1000111011,A计数器二进制为111000,对应分频比36 600,N计数器二进制为1000111011,A计数器二进制为111000,其余类推。R计数器、N计数器、A计数器可预置,各管脚接地为逻辑0,悬空为逻辑1。

2.3外围电路参数设计

假设压控振荡器控制电压△Vd=10 V,鉴相灵敏度Kd=9/2πV/rad,ζ值的大小直接影响环路的瞬态特性,ζ值大,环路的低通特性性能变差,对输入频率成分滤出能力降低;ζ值太小,瞬态特性有较大的过冲,捕捉时间加长,故需折衷考虑ζ的取值,通常比较合适的数值为ζ=0.5~1.5,通常选择最佳值1。

ωn为环路自然谐振角频率,ωn值的选择将直接影响环路滤波特性和捕捉时间,为了保证环路对噪声有较好的抑制,ωn应该远小于鉴相频率ωd,通常可按下式选择ωn=

- 全数字锁相环的设计及分析(03-01)

- 一种大电压输出摆幅低电流失配电荷泵的设计(04-22)

- 锁相环同步检波技术及在视频检波中的应用(05-20)

- 一种基于CMOS工艺的电荷泵锁相环芯片的设计(05-21)

- 基于锁相环的频率合成电路设计(07-30)

- 锁相环相位噪声与环路带宽的关系分析(08-04)