8 bit 800 Msps高速采样保持电路的设计

随着数字技术的突飞猛进,越来越多的电路系统将A/D转换器作为一个子模块集成到系统内部。例如在便携式数据传输、数字视频和图像处理等应用系统中,8~12 bit分辨率的嵌入式A/D转换器就是这些系统中一个非常重要的组成部分,采样保持电路(SH)是数据采集系统。而A/D转换器是最重要的组成部分之一,其性能直接决定着整个A/D转换器的性能。随着无线通信的迅速发展,要求数据的传输越来越快,复杂度不断提高的调制系统和电路使A/D转换器的采样频率逐渐接近射频的数量级。在这样高速的要求下,SH的作用就显得更加的重要,因为它可以消除A/D转换器前端采样级的大部分动态错误。

本文介绍了一种基于SiGe BiCMOS、开环全差分结构的SH。采样速率可以达到800 Msps,采样精度可以达到8 bit,能够适应无线通信领域的要求。

1 电路设计

1.1 电路总体结构

SiGe BiCMOS工艺具有高速、低功耗、低成本、高集成度的优势,能够很好地满足本设计对SH设计指标的要求,故设计工艺选定为SiGeBiCMOS。

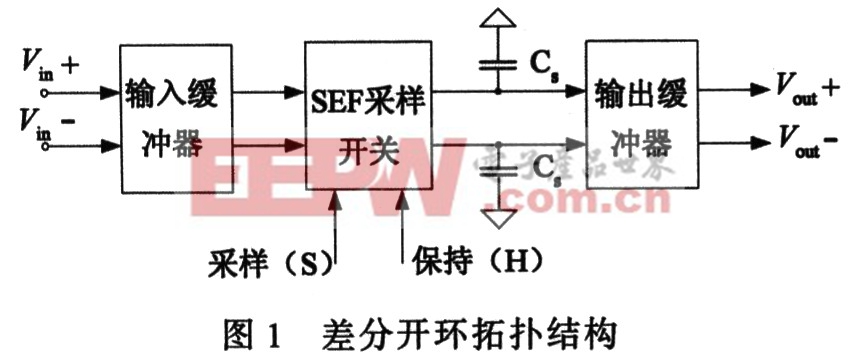

采样速率和精度要求的不同,决定了采样电路拓扑结构。尽管闭环结构的SH可以取得很高的精度,但是这种拓扑结构的SH频率响应较差。开环结构的SH常用在高频,为了达到较高的采样速率,应选择开环结构。开环结构的SH通常由一个输入缓冲器(IB),一个带有采样电容的开关和输出缓冲器(OB)组成。

考虑SH的采样精度为8 bit,采样速率为800Msps性能指标的要求,差分结构能保证很好的噪声性能,最终选择了如图1所示的全差分开环结构,其中包括输入缓冲器、采样开关、采样电容和输出缓冲器。采样开关采用开关射极跟随器(SEF)结构,输入缓冲器提供反向隔离减少输入端的开关噪声,输出缓冲器用来驱动ADC。由于电路是全差分结构,电路完全对称,为了更清楚地说明问题,图2仅给出了单端电路,即整体电路的一半。将两幅图2对称地接成全差分结构即是本设计的最终电路。

1.2 电路分析

1.2.1 输入缓冲器

输入缓冲器的主要目的是将信号源与采样部分分离,该电路的输入电容一般都比较大。输入缓冲器不能引入失真,且必须有一定的速度。理想的输入缓冲器应当具有大带宽、低噪声、高线性度和单位增益等特点。图2中的Q3、Q4、Q5的结构在采样时钟的控制下能够实现很好的隔离效果;Q1实现电压提升的作用。

1.2.2 SEF采样开关

本设计中使用的开关是开关射极跟随器,SEF既可以在高速度下运行,又可以保持很好的线性度。

在图2中,Q6、Q7、QS、I5是开关的主要部分。采样模式时,S相对于H是高电位,开关导通,I5流过QS和Q7。保持模式时,H相对于S是高电位,开关关断,I5经过Q6,此时QS的基极电位被拉得很低,所以关断。

谐波直接关系到电路的采样精度。整个电路是全差分结构,所以只考虑奇次谐波,其中三次谐波是最大的谐波,直接决定SFDR(无杂波动态范围),从而决定采样精度,采样精度的近似计算公式如式(1)。ENOB表示有效位

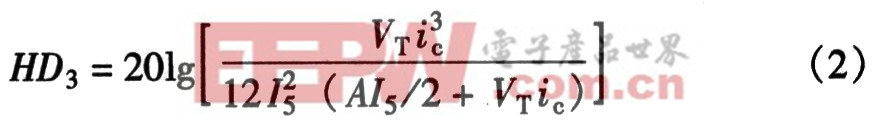

开关部分对电路的三次谐波影响最大,三次谐波的计算公式为

式中:VT是热电压;I5是图2中开关的电流;A是输入信号的幅度;ic=2πAfinC5,fin是输入信号的频率。

从式(2)中可以看出,要减小三次谐波就要选择较大的I5、较小的A、fin和CS。但是选择较大的I5会增加功耗,引入更大的噪声;较小的A、fin会减小输入信号的可用范围,限制采样频率(特别是在每周期相干采样2个点的最严酷情况下);较小的Cs会增加噪声(kT/C)。所以要获得良好的电路性能就要折中考虑这些因素,同时还要考虑本文随后介绍的其他影响。本设计中VT=26 mV,A=1 V,fin=387.5 MHz,Cs=450fF,I5=1.46 mA,得HD3≈-54.6 dB,可见理论值与一52.8 dB的实际值比较接近,电路性能可以满足要求。

图2中PM2、Qclp是一种电压稳定结构,将在后面介绍。Rs是为了改善输出电压的振铃减小建立时间而加入的一个小电阻。

1.2.3 输出缓冲器

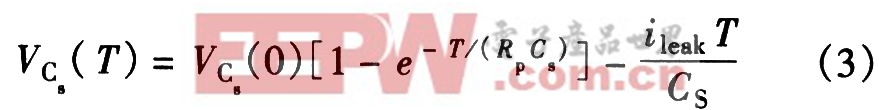

在图2中,以QOUT形成的射极跟随器是输出缓冲器的主体部分,用Q8、Q9、Q10组成单位增益放大器。因为目前的器件都会有漏电流,所以在输出缓冲器前有漏电流的存在,在保持模式时存储在采样电容CS上的信号电压不恒定。假设保持模式的持续时间为T、保持模式开始时CS上的电压为VCs(0)、保持模式结束时Cs上的电压为VCs(T),则

有

式中:ileak为漏电流;Rp为输出缓冲器的输入阻抗。

漏电流的存在会产生偏移误差和增益误差,如果漏电流是输入的非线性函数,将产生失真。但是因为使用了射极跟随器,所以Rp=rb+βrce,式中β是Vce的非线性函数,所以由下垂率导致的误差表现为输入电压的非线性函数,也就是说产生了谐波。为了抑制这种谐波,用Q8、Q9、Q10组成单位增益放大器以增大输入电阻Rp,减小漏电流。

1.2.4 保持模式馈通(HMF)的改善

在保持模式下,由于信号通路上晶体管存互寄生电容(图2中Cbe,Qs),输入信号与保持在采样电容上的信号之间并非百分之百的隔离,导致被保持在采样电容Cs上的信号受到输入信号影响,而存在失真。在保持模式下,由于电容Cbe,Qs和Cs非线性的分压作用,一小部分的信号出现在输出端上。因此

- 14位125Msps模数转换器ADS5500及其应用 (03-06)

- 如何收敛高速ADC时序(03-09)

- 9位100 MSPS流水线结构A/D转换器的设计(02-11)

- 逐次逼近型 ADC:确保首次转换有效(03-20)

- 集成低功耗输入驱动器和基准电压源的16位6 MSPS SAR ADC系统(02-27)

- 具有抗混叠滤波器和184.32 MSPS采样速率的高性能中(04-23)