基于柔性多层绕组的集成EMI滤波器

摘要:本文提出一种基于柔性多层集成L-C绕组的新型EMI滤波器集成结构。 通过采用此种结构,可以将共模电感,差模电感与共模电容集成为1个单元。与平面PCB绕组的集成EMI滤波器比较, 具有铜损显著减小的特点。本文还介绍了实验样机和实验结果。 叙词:柔性多层绕组 EMI滤波器 无源集成 平面PCB Abstract:This article introduces a new EMI filter integration structure based on flexible multi-layer L-C wiring. The application of this structure will integrate common-mode choke, differential-mode choke and common- mode capacitance into one unit. Compared with integrated EMI filter based on plane PCB wiring, it greatly lowers the copper loss. This article also presents an experimental sample and experimental results. Keyword:Flexible multi-layer wiring, EMI Filter, Passive integration, Plane PCB

1、简介

随着电力电子技术的发展,开关电源的工作频率越来越高,由此带来的电磁干扰(EMI)问题也日益严重。为了防止EMI发射水平超过相关的标准,通常会采用EMI 滤波器。在一个前端变换器中,传统形式的EMI 滤波器通常要占整个电源体积的15%~20%。由于要求开关电源的体积将越来越小,EMI 滤波器的尺寸也同样需要减小。

鉴于此,Van Wyk, J.D.提出一种电磁集成结构的EMI滤波器[1]~[3]。通过采用平面PCB绕组电感电容的集成结构,把所有的无源元件均集成到一个单元中。在这种结构中,需要使用一个体积较大的磁芯。J. Biela 提出一种无源集成结构和混合有源集成结构[4],可以减小磁芯的高度和尺寸,但是整个滤波器的面积大大增加,而且效率降低。

前述的这些集成EMI滤波器的方法均是基于平面PCB集成绕组结构。本文提出一种新型EMI滤波器结构,基于柔性多层带材绕组的电感电容集成结构。并制作了一个样机,作为1000W,220V/50Hz输入,DC48V输出前端变换器的EMI滤波器。给出了实验结果。

2、平面PCB绕组与柔性多层带材绕组比较

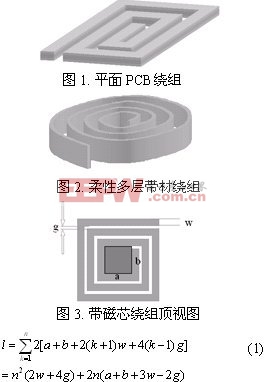

平面PCB绕组与柔性多层带材绕组分别如图1、图2所示。他们的基本结构均由两层导体与中间的介质层组成,而把这种绕组绕在磁心上时,可以实现电感电容的集成元件。

图3为这两种绕组绕于磁心上时的顶视图,其中w是绕组宽度,g为相邻匝之间的距离,a和b分别为矩形磁心柱截面的边长。另外,定义n为匝数,h为绕组的高度。

由此可以得到绕组总长度的计算公式如下:

在实际应用中,平面PCB绕组的宽度w比高度h要大得多,而对于柔性多层带材绕组来说,w则远远小于h。且由于工艺与绝缘的要求,平面PCB的匝间距离g也远远大于柔性多层带材绕组。如果两种应用的磁心相同,绕组匝数相同,从公式(1)我们可以看出平面PCB绕组的总长度将比柔性多层带材绕组长度要大得多,而且随着匝数n的增加,差距越大。

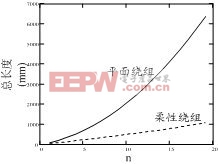

图4. 两种绕组长度比较

通过图4可以更清楚的看到这一点,这里假设a=b=10mm,而其他参数如表1所示。可以看到,随着匝数的增加,柔性多层带材绕组在长度上的优势就越明显。绕组越长意味着用铜量越大,损耗也越大,可能也导致体积越大。因此,这是柔性多层带材绕组应用于无源元件集成的一个重要优点。

3、集成结构

如图5所示为一种柔性多层带材的图形描述,由两层导体、一层介质及一层绝缘组成。当把这种带材绕制在磁心上,就可以同时得到一定的电感和电容。

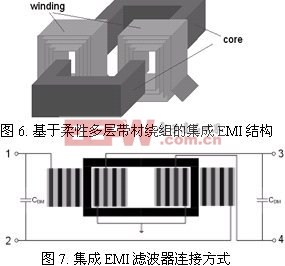

我们提出的基于柔性多层带材绕组的集成EMI结构如图6所示。采用一组UU(或UI)磁心,在磁心的两个柱上分别绕了一个柔性多层带材绕组。这样的一种结构可以把共模电感、差模电感和共模电容集成为一个元件。按照图7所示的连接方法,加上外加的差模电容,就可以得到一个完整的EMI滤波电路。

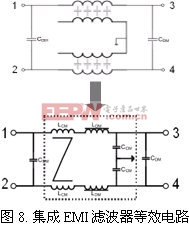

集成EMI滤波器的等效电路如图8所示,虚线框中的电路部分为集成元件的等效电路。两个柔性绕组通过磁心形成的闭合磁路耦合形成共模电感LCM,每个绕组中的两层铜箔与中间的介质层形成共模电容CCM,且由于差模电感通常只有共模电感1%大小,所以可以利用两个绕组漏感实现。而如果漏感比所需要的差模电感小时,可以采用一些增大漏感的方法。

如图9所示给出了4种增大漏感的方法。图9(a)在基本结构的顶部增加一个U形磁心,它的边柱上分别绕有若干匝导线用于实现差模电感,它与基本结构的主磁心公用一部分磁路。采用这种方法可以很容易的得到所需的差模电感,代价是整个滤波器的高度和体积都有所增加。由于可以利用漏感来实现DM电感,所以可以采用一些减小两个柔性绕组之间的耦合系数的方法,使得

- 开关电源EMI设计小结(01-18)

- 解析几种有效的开关电源电磁干扰的抑制措施(01-22)

- PWM控制电路的基本构成及工作原理(02-23)

- 将EMI/EMC控制在摇篮之中(06-25)

- SiGe 功率放大器为嵌入式WLAN 提供业界占位面积最小的解决方案(11-18)

- 意法半导体微型滤波器降低音乐手机蜂窝噪声(11-24)