转换器时钟技术向高速数据时钟发展

无线基础设施、宽带和仪器仪表应用通常需要高性能的时钟电路,它们主要需要时钟的器件是高速数据转换器。这些系统的时钟电路所需的几个关键性能指标包括低相位噪声和抖动、精确的频率转换和去抖动能力。高性能转换器时钟解决方案所体现的许多属性可被有线网络所用的时钟解决方案延用。整个有线网络对互操作性和可靠同步的需求也衍生出某些独特的时钟系统需求。希望这篇文章有助于对这两个应用领域的时钟技术需求进行对比和分析。

转换器时钟

基站收发器、宽带调制解调器和高端仪器仪表通常需要具有高动态范围和高采样率的ADC和/或DAC。高动态范围是为了将信号解析到所需的精度。高采样率则是处理高带宽信号所必需的。无论是无线电系统、调制解调器或者是测量仪器,对转换器的要求将取决于整个系统的规格参数和架构。该转换器的采样时钟的频谱纯度往往会对实际达到的性能产生重大影响。

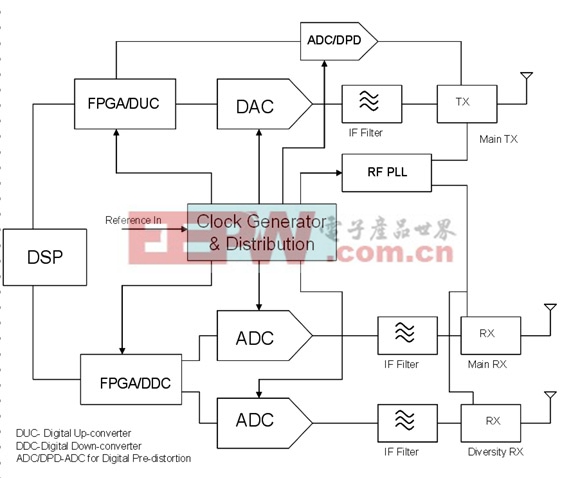

一个无线收发器电路的例子如图1所示。除了为ADC和DAC提供时钟,时钟发生器还负责将时钟信号分配到收发器卡上的其他几个电路模块。接下来我们将集中讨论时钟抖动和相位噪声对ADC性能的影响。

图1:收发器系统框图。

无线电接收器中ADC的一个关键指标是信噪比(SNR),它将影响到ADC在给定幅度范围内能够达到的信号采样精度。理想情况下,ADC应该能够以很高的分辨率将非常小的模拟输入信号转换成精确的数字信号。按照无线电术语,ADC的SNR将决定最小可检测信号(MDS)。

N位转换器基于量化噪声的理论SNR等于:

SNR = 6.02(N) + 1.8 db

因此,对于一个14位转换器,其可以实现的最佳SNR大约为86db。

在IF采样架构中,如图1所示框图,对时钟抖动的要求可以说非常严格。事实上,提供给ADC的时钟的质量常常是系统SNR性能的一个限制因素。这可以通过以下公式来理解。

这个公式定义了采样时钟的宽带抖动与ADC在某一给定模拟输入频率抖动情况下可以达到的最大SNR之间的关系。举例来说,如果采样时钟的宽带抖动为275fs ,对170MHz的中频信号采样时,SNR基本上不会高于70.65db。

实际上,ADC内的其他噪声机制通常会将SNR值限制在低于理论水平或量化噪声(公式1) 。这一内部噪声是由于模拟信号路径和采样时钟路径中的器件热噪声而引起的。采样时钟路径中的器件噪声有效地转换为相位调制噪声,又称为孔径抖动。这种行为就像外部时钟上的抖动,遵循公式2 ,孔径抖动(taperture-jitter)代替时钟抖动(tclock-jitter)。由公式2可以看出,随着采样的IF频率(fanalog)增加,SNR下降。

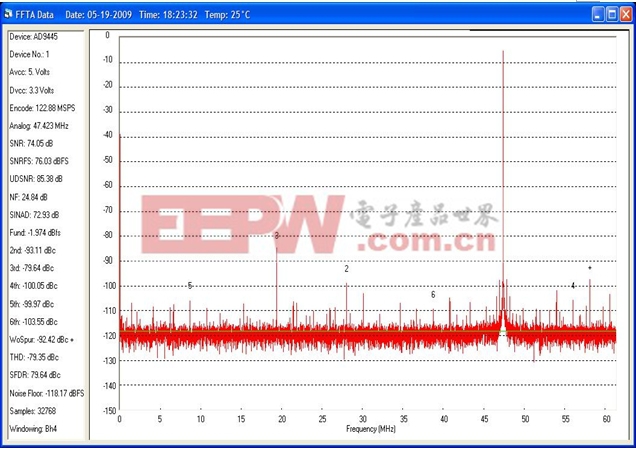

外部时钟的频谱纯度与ADC可实现的SNR之间的关系,可以通过以下一组实验室测量数据进行表述。图2显示了14位ADC采样170MHz中频信号的FFT波形。在这种情况下所用的外部时钟是源自频谱纯净的Wenzel实验室参考振荡器,驱动着带高压摆率输出信号的低抖动矩形波整形电路。测量的意图是尽量减少时钟的影响,并确定由于ADC效应所达到的SNR。由此产生的相对满量程输入信号的SNR测量数据,在图中标示为SNRFS,是76db。这与ADC数据手册1是一致的。Wenzel实验室参考振荡器的确会对SNR有一定影响,但所测的SNR主要是受ADC量化噪声和内部ADC孔径抖动的共同影响。

图2:14位ADC的FFT波形。模拟输入频率= 170MHZ,时钟频率= 122.88MHz。SNRFS =76db。

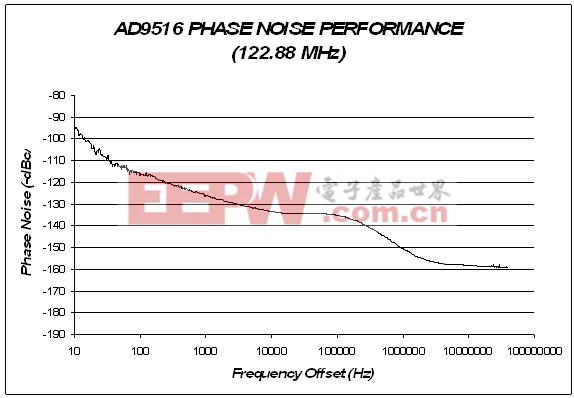

现在,我们将使用一个适合实际收发卡时钟应用的内置VCO的时钟IC。为了估算这一时钟信号对ADC性能产生的影响,我们可以先测量时钟电路的相位噪声。其相位噪声曲线如图3所示。

图3 :时钟IC在122.88MHz下的相位噪声

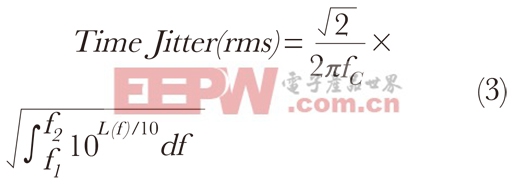

在给定的频率范围内,我们可以使用下列公式来将相位噪声转换成时间抖动。

该公式本质上是对相位误差在目标频率范围内进行积分并从一个相对2π的积分弧度误差转换成均方根时间误差。

将图3的相位噪声数据代入公式3,在50kHz至61MHz的频率范围内,会得出230fs的抖动值。50kHz至61MHz频率范围是用来对应有效的FFT测量范围,后者将用于检验抖动对所测SNR的影响的估算是否准确。低至50kHz是源于FFT的有效二进制间距,高至61MHz是奈奎斯特频率。将得出的230fs抖动代入公式1则得出72.2db的SNR值。

然而,实际达到的SNR将受到该抖动和固有ADC噪声的共同影响。图2 FFT波形的SNR(76db)与根据时钟抖动得出的估算值(72.2db)的和平方根将得出70.68db的复合SNR。

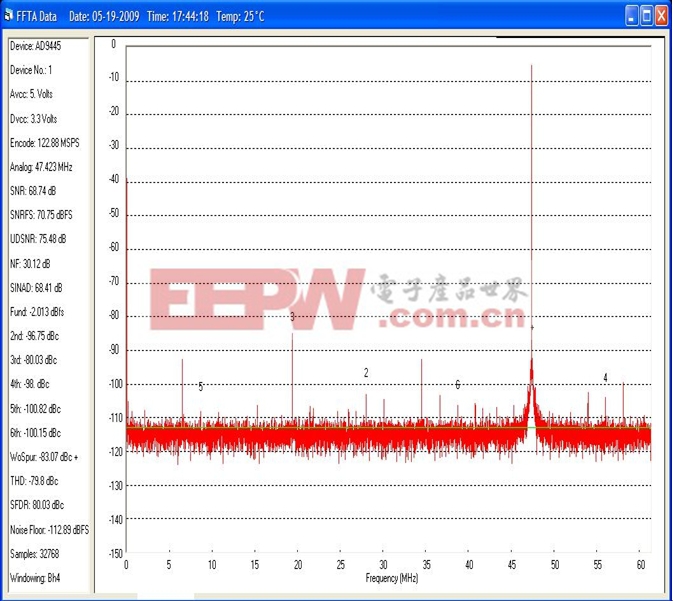

为了检验这一估算值,图4显示了采用此时钟IC作为采样时钟的相应ADC FFT波形。所达到的SNR接近基于时钟抖动的估算值,体现了时钟抖动对ADC性能的影响至关重要。

图4:采用时钟IC的14位ADC的FFT波形。模拟输入频率= 170MHZ,时钟频率= 122.88MHz。SNRFS =70.75db。

- RS-232至RS-485RS-422接口的智能转换器(01-24)

- 同步降压转换器电路设计基础(01-01)

- 真有效值AC/DC转换器AD736及其在RMS仪表电路中的应用(02-16)

- 满足FPGA电源设计需求的DC/DC转换器(02-15)

- 开关DC-DC转换器的EMI方案(04-29)

- 多媒体手机的电源管理方案(04-26)