基于CPLD技术的PC104总线多功能扩展卡设计

1. 引言

目前,随着军事、工业、医疗、体育等领域的控制系统逐渐向着嵌入式、小型化、集成化方向发展,以嵌入式主板为主控模块的嵌入式控制系统获得了长足发展。PC104总线嵌入式主板以尺寸小、低功耗、易扩展、高集成度、高可靠性以及开发环境优异(多种操作系统支持)等优点在这些领域获得广泛应用。但是,在采用PC104总线嵌入式主板设计控制系统时,PC104总线扩展板卡种类不多且功能比较单一,设计人员往往需要选择各种不同功能的板卡组合使用,既造成了资源的浪费及设计成本的提高,又导致了控制系统的体积增加及可靠性降低。为此,我们设计了这款集成度较高的PC104总线多功能扩展卡。

该多功能扩展卡是针对国家体育总局奥运科技攻关项目“帆板摇帆训练测试系统研究”设计的。采用ALTERA公司的ACEX1K系列复杂可编程数字逻辑器件(CPLD)――EP1K50TI144-4作为主控芯片,集成了8路12位高速模拟量输入、2路12位模拟量输出、12路带光电隔离的24V开关量输入/输出及一个正交解码电路。设计时的通用性考虑使其可作为各种型号的PC104总线嵌入式主板(如3寸主板PCM-5820)的扩展卡。主板CPU可通过总线直接访问多功能扩展卡的各个功能电路,访问协议与台湾研华的PCL-818HG、PCL-727板卡兼容。

2. 基于CPLD技术的PC104总线多功能扩展卡的硬件设计

多功能扩展卡的硬件设计包括电路板硬件设计和CPLD内部硬件设计。

2.1 多功能扩展卡的电路板硬件设计

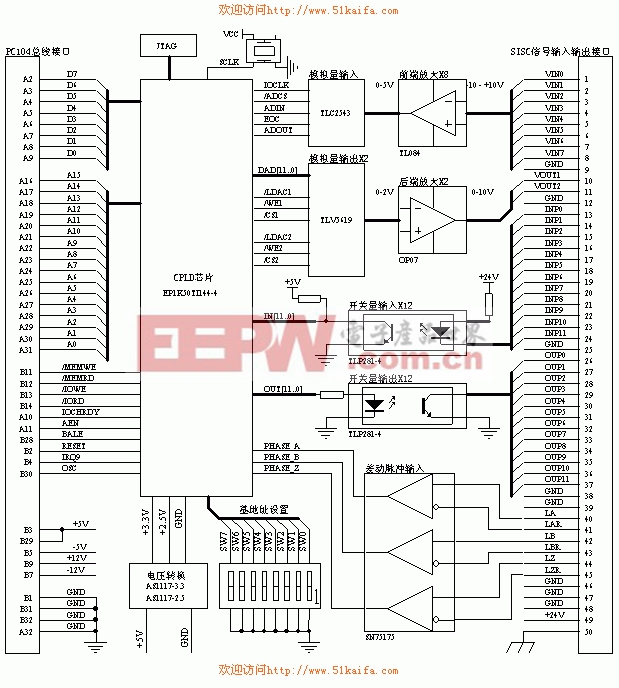

多功能扩展卡的电路板硬件设计包括:主控电路、模拟量输入电路、模拟量输出电路、带光电隔离的开关量输入/输出电路及正交解码输入电路。系统原理框图如图1所示。

图 1 多功能扩展卡电路板硬件设计系统原理框图

2.1.1主控电路

主控电路由一片CPLD芯片及其编程配置电路(JTAG)、电压转换电路组成。

CPLD芯片采用ALTERA公司的ACEX1K系列的复杂可编程数字逻辑器件――EP1K50TI144-4。该芯片具有在线可编程功能,内部集成逻辑可通过编程配置电路(JTAG)在线下载,保证了设计的灵活性。电压转换电路提供芯片的工作电压2.5V(内核电压)和3.3V(I/O电压)。

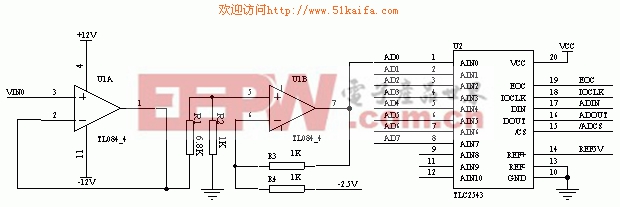

2.1.2 模拟量输入电路

多功能扩展卡提供了8路单端模拟量输入,模拟量输入电路由一片12位串行A/D转换器TLC2543及8路前端放大电路组成。电路原理图如图2(前端放大电路只介绍一路)所示。前端放大电路的功能是将-10~10V的模拟信号转换成0~5V的模拟信号。

图2 多功能扩展卡模拟量输入电路

2.1.3 模拟量输出电路

多功能扩展卡提供了2路模拟量输出,模拟量输出电路由两片12位并行D/A芯片TLV5619及后端放大驱动电路组成。后端放大电路的功能是将D/A芯片的0~2V的输出信号放大到0~10V,并提供一定的电路驱动能力。

2.1.4 开关量输入/输出电路

多功能扩展卡提供了12路低电平有效、带光电隔离的24V开关量输入/输出,光电隔离芯片采用TLP281-4。

2.1.5 正交解码输入电路

正交解码输入电路是一片单电源、四路差分输入接收芯片SN75175。接收来自交流伺服电机驱动器的两路正交差动光电编码器输出信号,并将其转换成TTL电平,保证了高速、高可靠性的远距离信号传输。

2.2 多功能扩展卡的CPLD内部硬件设计

多功能扩展卡的CPLD内部硬件设计包括:地址分配及译码电路、A/D模块控制电路、

D/A模块控制电路、开关量输入/输出模块控制电路和正交解码模块控制电路。

2.2.1 地址分配及译码电路

地址分配及译码电路包括基地址发生电路和地址译码电路。在与嵌入式主板组成系统时,相对于嵌入式主板而言,多功能扩展卡是一个外围设备,因此,首先要为该卡设置一个与系统内的其他外围设备不相冲突的基地址,这由扩展卡的基地址设置开关及CPLD内部地址分配及译码电路完成。地址分配及译码电路由数值比较器74688、译码器74154等构成,

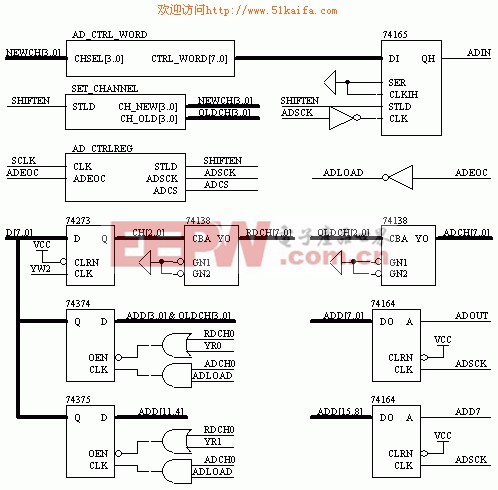

2.2.2 A/D模块控制电路

A/D模块控制电路的控制逻辑由两部分组成:其一是实现嵌入式主板通过总线访问各模拟通道的A/D转换结果,由模拟通道选择寄存器(74273)、转换数据寄存器(74374)等构成;其二是提供A/D芯片的接口时序,实现A/D芯片八个通道的自动采样和转换,由串/并数据转换逻辑(74164)、并/串数据转换逻辑(74165)、通道扫描控制逻辑(AD_CTRL_WORD)、A/D控制时序逻辑(AD_CTRLREG)等构成。A/D模块控制电路的电路设计如图3所示(转换数据寄存器只介绍一路)。

图3 多功能扩展卡A/D模块控制电路

2.2.3 D/A模块控制电路

D/A模块控制电路由74373 IP软核及相应控制逻辑构成,功能是同时刷新D/A芯片的输入值。D/A控制模块电路采用两级锁存电路刷新D/A芯片的输入值,先置高4位字节数据,再置低8位字节数据,置低字节数据的同时使能D/A芯片的片选信号(/CS)、写信号(/WE),然后置数据锁存信号(/LDAC),刷新D/A的输出。

- 基于DSP和CPLD的移相全桥软开关电源数字控制器(06-02)

- 基于CPLD的MIDI音乐播放器的设计(06-16)

- 基于CPLD的电器定时开关控制系统设计(08-17)

- 基于CPLD和VS1011E解码器的电梯语音系统设计(11-26)

- 基于DSP和CPLD的软开关电源数字控制器(01-14)

- ADS8323与高速FIFO接口电路的CPLD实现(03-26)