一种双DSP系统串行引导方案的实现

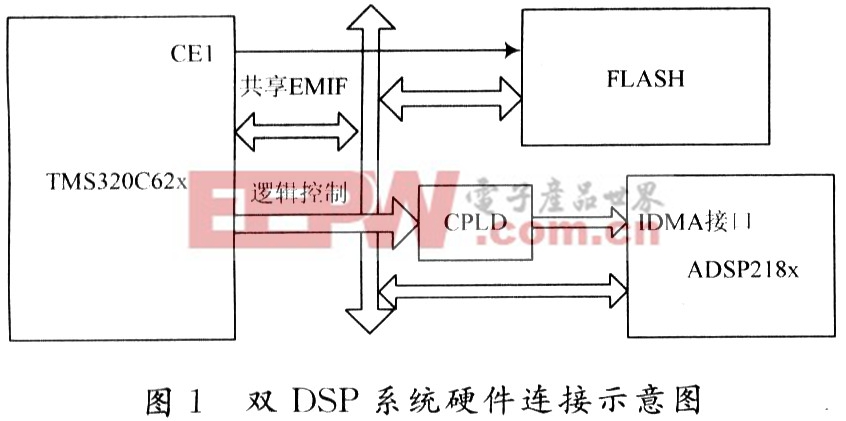

在某型光电跟踪产品中,由于需要对抗各种人工干扰和背景干扰,使得导引系统需要处理的信息量成倍增加,对导引系统的实时处理性能提出了更高的要求。针对这种情况,导引系统采用了双DSP系统的信息处理方案,DSP选用AD公司的ADSP218x和TI公司的TMS320C62x。ADSP218x进行目标信号的采样和外围控制信号的输入、输出,TMS320C62x专门进行目标的鉴相、各种抗干扰算法的计算,这样TMS320C62x不受外设服务中断影响,可以更好地发挥计算效率,提高了导引系统的实时处理性能。本文针对ADSP218x系列和TMS320C62x系列组成的双DSP系统,提出了一种串行引导方案,同时给出了其硬件及软件的具体实现方法。

1 DSP引导模式

1.1 TMS320C62x引导模式

TMS320C62x系列DSP提供了三种引导方式:

(1)无引导过程:DSP直接从地址0开始执行代码;

(2)ROM方式引导:由DMA/EDMA控制器从外部CE1空间中的ROM中拷贝固定数量的代码到地址0,启动时也可选择ROM的宽度,拷贝结束后,CPU从地址0开始运行;

(3)HPI方式引导:由外部主机通过HPI对芯片的存储器空间进行初始化,初始化结束后,外部主机通过HPI中断唤醒TMS320C62x,CPU开始从地址0运行。

所有这些设置项都是在芯片复位的时候才进行检查。一旦复位信号有效(reset=0),所有的三态输出管脚恢复为默认状态,然后在reset信号的上升沿处检查设置管脚BOOTMODE[4:0]的状态,自举逻辑开始生效。

1.2 ADSP218x引导模式

ADSP218x系列DSP提供了三种引导方式:

(1)无引导过程:DSP直接从地址0开始执行代码;

(2)BDMA方式引导:复位后DSP以BDMA方式首先从字节存储空间拷贝前32字的程序代码,拷贝完程序从程序存储地址0开始执行代码。

(3)IDMA方式引导:复位后DSP以IDMA方式可以存取任意数量的内部存储空间,当内部程序存储地址0被写入时,程序从程序存储地址0开始执行代码。

以上设置都是在芯片复位的时候才进行检查,当复位信号有效时(reset=0),所有的三态输出管脚恢复为默认状态,然后在reset信号的上升沿处检查设置管脚MODE[A:D]的状态,自举逻辑开始生效。

1.3 双DSP系统串行引导模式

根据以上两种DSP的引导模式,选用串行引导模式,即把TMS320C62x作为主处理机,外围接8位宽的FLASH,采用ROM方式引导,TMS320C62x和AD-SP218x的程序都固化在FLASH中,ADSP218x作为从处理机,采用IDMA方式引导,并且两个DSP之间的通讯也采用IDMA方式。这样TMS320C62x可以把ADSP218x作为一个存储区来访问,既去掉了握手软件,提高了工作效率,又可以去掉ADSP218x外围的FLASH,减少了硬件花销。主要硬件连接示意图如图1所示。

双DSP系统串行引导的过程如下:系统上电后,TMS320C62x从位于CE1空间FLASH中以ROM引导的方式复制一定数量的TMS320C62x程序至地址为Ox00000000的内部程序存储空间。当程序复制完毕后,TMS320C62x开始从0x00000000起始的程序地址开始执行程序,利用这段程序,把剩下的程序从FLASH中读出,TMS320C62x进入到正常工作状态。然后TMS320C62x负责将存储在FLASH中的ADSP218x的运行程序读出,通过IDMA接口发送至ADSP218x的片内PM存储区,执行对ADSP218x的程序装载。当ADSP218x引导完毕后,ADSP218x运行装入的程序进入正常的工作状态,至此系统串行引导完毕。

2 双DSP系统串行引导的实现

2.1 硬件连接

TMS320C62x的低16位数据线ED15~0与ADSP218x的IAD15~0连接,TMS320C62X的低8位数据线ED7~0与FLASH的数据线D7~0连接。TMS320C62x的BOOTMODE[4:0]引脚配置如下:

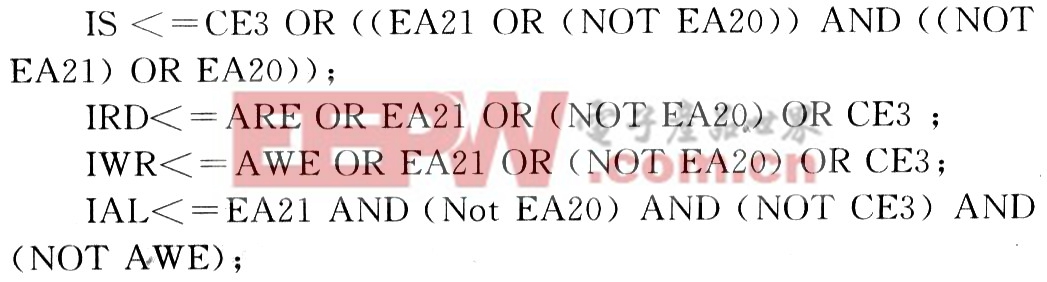

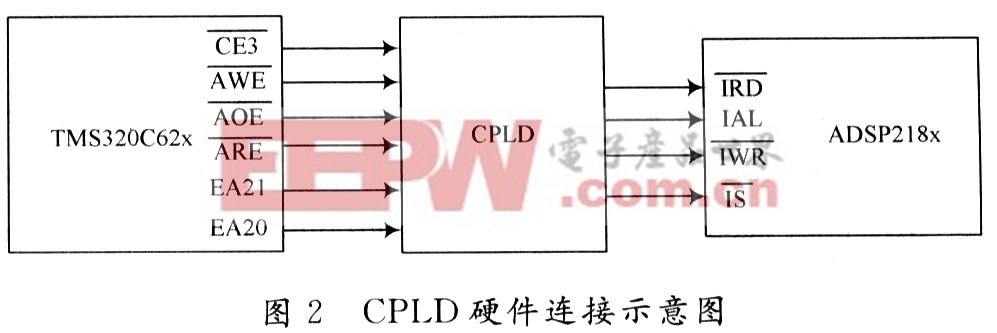

由于TMS320C62x与ADSP218x的IDMA通讯控制需要译码,因此加了一片CPLD,硬件连接图如图2所示。片内的逻辑方程为:

2.2 TMS320C62x启动程序代码的创建

TMS320C62x启动程序代码包含以下几个部分。

2.2.1 中断向量表vectors.asm

中断向量表缺省保存在TMS320C62x内部RAM的从0地址开始长度为0x200字节的空间,上电或复位后,芯片自动运行复位中断。因此,复位中断向量中应包含跳转到引导程序(_boot)的语句,引导程序的主体在boot.asm中定义。部分程序如下:

2.2.2 自引导的汇编程序boot.asm

自引导汇编程序主要是配置基本的寄存器,并将保存在外部FLASH中的二进制程序拷贝到DSP内部的RAM中再执行。汇编程序如下:

2.2.3 主程序main.c

主程序是DSP要实现具体功能的主体,其定义的主函数main()经编译后在函数_c_int00中调用,因此在上面的引导程序结束时,将跳转到函数_c_int00,即主函数main执行。另外在主程序中,还要包含把ADSP218x的应用程序从FLASH传送到ADSP218x内部存储区的子程序。

2.2.4 链接命令程序link.cmd

链接命令程序用于定义DSP系统各存储区的开始地址及大小,并分配编译后各段到相应的存储空间,link.cmd内容如下:

- 单片式降压型稳压器为DSP提供片内电源排序(01-09)

- 什么是PCI总线?其接口芯片的应用(01-26)

- 功率分配系统(PDS)设计:利用旁路电容/去耦电容(04-29)

- 具有多个电压轨的FPGA和DSP电源设计实例(05-22)

- 具有多个电压轨的FPGA和DSP电源设计实例(二) (05-22)

- 基于DSP和CPLD的移相全桥软开关电源数字控制器(06-02)