采用IDDR的亚稳态问题解决方案

什么是亚稳态

在FPGA等同步逻辑数字器件中,所有器件的寄存器单元都需要预定义信号时序以使器件正确地捕获数据,进而产生可靠的输出信号。当另一器件将数据发送给FPGA时,FPGA的输入寄存器必须在时钟脉冲边沿前保证最短的建立时间和时钟脉冲边沿后的保持时间,从而确保正常完整地 接收信号。

在一定的延迟后,寄存器输出端随后将信号发送到FPGA的其他部分。不过,如果信号传输违反了指定时间要求,那么输出寄存器可能就会进入所谓的亚稳态,这就导致寄存器输出值会在高低状态之间波动,且这种状态的时间不确定,从而使稳定输出状态无法达到寄存器指定的时间,进而造成性能略有延迟或逻辑行为的副效应。

解决问题

一般来说,将FPGA连接到另一个具有不同时钟域的数字器件时,必须给FPGA的输入部分添加一级同步,使FPGA时钟域中的第一个寄存器充当同步寄存器。为了实现这一目的,可在FPGA器件的输入级中使用一系列寄存器或同步寄存器链。该链可在输入寄存器将信号发送到FPGA的其他区域之前,允许 能有更多的时间解决潜在的亚稳态信号问题。亚稳态信号的稳定时间通常比一个时钟周期要短得多,因此即便延迟半个时钟周期,亚稳态出现的概率也会按数量级减少。

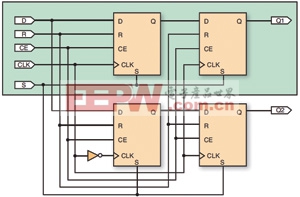

为了降低亚稳态问题的出现概率,在设计中实现的一系列寄存器(连接成移位寄存器)必须满足以下标准要求:

所有寄存器必须由同一时钟,或与同一时钟相位相关的时钟控制。

链中每个寄存器的扇出都仅针对相邻的寄存器。

由于不能完全消除亚稳态问题,因此必须做好解决问题的准备。为此,设计人员采用平均故障间隔时间(MTBF)这个指标来估算从问题出现并导致故障的两个事件间的平均时间。MTBF值越高,说明设计的稳定性越高。如果发生了“故障”,只是说明没有解决亚稳态问题,并不是系统本身真的出现了故障。

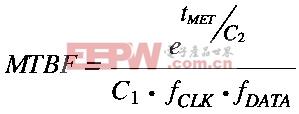

可用以下方程式计算出寄存器的MTBF:

在本例中,C1和C2代表寄存器技术相关常数,tMET代表亚稳态的稳定时间。

可根据每个寄存器的MTBF,确定总的MTBF值。同步器的故障率为1/MTBF,则将每个同步器的故障率相加,就能计算出整个设计的故障率:

从上式可以明显看出,通过改进寄存器单元的架构,优化设计以延长同步寄存器的tMET,甚至增加链中寄存器的数量等多种方法来改进MTBF。

高层代码与布局图

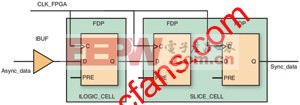

如果发现输入信号存在潜在的亚稳态问题,只需创建与同一时钟有相位关系的时钟驱动的寄存器链就能解决此问题。这需要提供如图1所示的电路。

图1 同步器链的默认布置图

图中,将寄存器链放置在两个单元中:第一个为ILOGIC单元,而另外两个寄存器放置在SLICE单元中(选择具有相同时钟的3个寄存器和链)。这是减少亚稳态问题的一种快速且非常简单的方法,还有其他一些方法不但可减少亚稳态问题,还可优化性能。

使用赛灵思逻辑块的IDDR方法

在Virtex-4和Virtex-5 FPGA中,赛灵思将其ILOGIC模块直接放置在I/O驱动器和接收器的后面。该模块包括4个存储元件寄存器和1个可编程绝对延迟元件。

Virtex-4与Virtex-5器件均采用这4个寄存器来实现双倍数据率输入(IDDR)寄存器,功能设计师只需例化IDDR原语便能实现。这将使 受益匪浅。

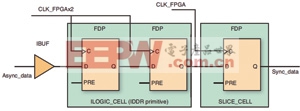

这种原语的其中一个模式称为SAME_EDGE_PIPELINED。图2显示了采用这种模式的DDR输入寄存器及相关信号。绿色矩形框显示了一系列最优的寄存器,可用其解决亚稳态问题。此外,使用 IDDR 方法还有一个优势,即能使用两三倍之多的主时钟,同时又不会造成任何设计时延问题。

图2 SAME_EDGE_PIPELINED模式中的输入DDR

只需少量代码

在《Virtex-4用户指南》的328~329页,举例说明采用VHDL和Verilog语言编写的IDDR原语的例化。以下采用Verilog语言的IDDR原码例化的典型实例:

defparam IDDR_INT2.DDR_CLK_EDGE = SAME_EDGE_PIPELINED;

defparam IDDR_INT2.INIT_Q1 = 1'b1;

defparam IDDR_INT2.INIT_Q2 = 1'b1;

defparam IDDR_INT2.SRTYPE = SYNC;

IDDR IDDR_INT2( .Q1(sync_data),

.Q2(signal_noload), .C(CLK_2X),

.CE(1'b1), .D(async_data),.R(), .S());

在图3中看到全新的布局图。 用这种方法将寄存器链放置在两个单元:前两个寄存器放置在ILOGIC单元中,另一个寄存器则放置在SLICE单元中(这里选择的链具有3个寄存器和2个不同的时钟,其中一个时钟速度是另一个的两倍)。

图3 显示IDDR替代的同步器链

整体而言,亚稳态问题会给设计带来不便,但采用一些快速便捷的解决方案(如以一种新的方式使用IDDR原语)就能大幅降低设计发生亚稳态问题的几率。大家应在创建设计时就采用上述方法,而不应事后亡羊补牢,这样就能创建出既能灵活应对

- 基于IDDR的亚稳态问题解决方案介绍(08-18)

- 数字触发器原理与亚稳态特性简介(06-23)

- 亚稳态的错误率问题分析(06-23)

- 亚稳态的错误率分析(06-22)

- 数字触发器原理与亚稳态特性(06-22)