亚稳态的错误率分析

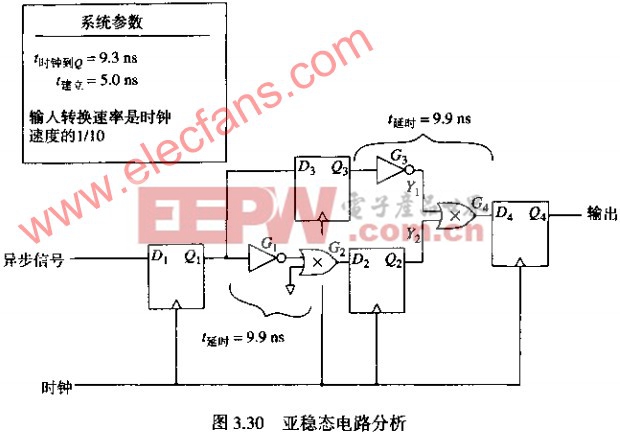

如图3.30所示,采用ACTEL ACT-1门阵列实现的电路,当输入电压变化时,其输出产生脉冲的概率有多大?简单应用同步逻辑理论,它永远也不会发生。但现在我们会更好地理解这个问题了。

首先检查最坏情况下建立时间:

TPD=9.3NS(时钟到Q1,建立时间很好)

TPD=9.3NS(反相器-异或门之和)

TSU=5.5NS/23.6NS(D2的建立时间)

任何小于42MHZ的时钟(23.6NS)都能满足传播时间和建立时间。Y1和Y2始终匹配,输出Q4永远也不会变成高电平。

电路唯一发生错误的可能是亚稳态使得Q1转换推迟,错过了D2的建立时间窗口(因为经G1和G2的传播延时),但Q1并没有错过D3。

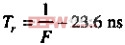

如果实际时钟F的速率小于42MHZ,我们可以算出Q1不错过D2建立时间窗口的严稳态延时预算。允许额外分配给亚稳态的为:

这个TR延时称为允许的判决时间。

Q1需要比TR更长的时间来达到稳定,这个亚稳态窗口是:

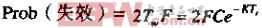

落在正负TW内,且在总的周期时间1/F之外的概率是:

ACTEL在1989年出版的“ACT-1 FANILY GATE ARRAYS PRODUCT GUIDE”列出了常数C和K。这里我们对两个进行调整,使之符合我们的单位体系:HZ和S。

以小时为单位的平均失效间隔时间,可以通过失效概率和输入信号的转换率R来计算得到。因为亚稳态仅仅在输入信号变化时发生,如果输入信号变化较快,则失效的概率也较大。

其中,MPBF=平均失效间隔时间,H

R=输入信号转换率真,HZ

PROB(失效)=在任意单个输入信号转换时的失效概率

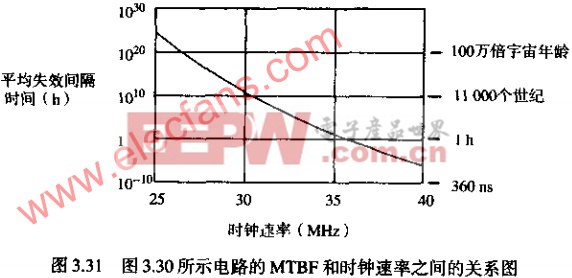

图3.31给出了MTBF与频率的关系图,这个图假定输入信号的转换频率时钟频率的1/10。在35MHZ时,失效概率是4*10的负12次方。如果电路每秒处理350万次输入,则每19小时发生一次失效。

- 基于IDDR的亚稳态问题解决方案介绍(08-18)

- 数字触发器原理与亚稳态特性简介(06-23)

- 亚稳态的错误率问题分析(06-23)

- 采用IDDR的亚稳态问题解决方案(12-02)

- 数字触发器原理与亚稳态特性(06-22)