鉴频鉴相器的指标对锁相环(PLL)死区及抖动性能的影

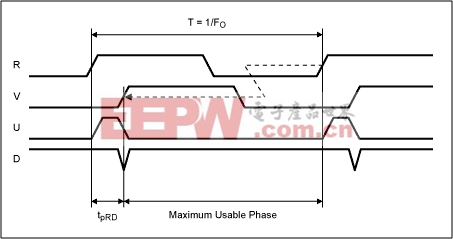

图7. 器件时序特性给出最大可用的相位限制

图7所示时序图描述了最大相位条件下的输入、输出波形。进一步增大超前输入相位,将导致随后的“V”输入上升沿被忽略,输出复位至差分低电平状态。鉴相器将响应接下来的输入上升沿,并将其作为超前波形。图7示例中,后续的边沿会出现在“R”输入,鉴相器响应是针对“R”超前“V”的条件得出的。

公式列表

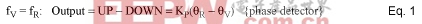

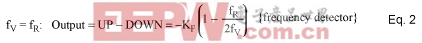

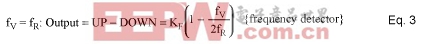

式1、式2和式3给出了输入频率相同条件下(锁定条件)和输入频率不同条件下(对应于fV > fR、fV fR)鉴相/鉴频器的传输函数。

其中:

输出(Output) = 鉴相输出

KP = 鉴相增益

ΘR = 参考信号相位

ΘV = 反馈信号相位

其中:

KF = 鉴频增益

fR = 参考信号频率

fV = 反馈信号频率

式4和式5给出了电荷泵和环路滤波器的传输函数。

其中:

OUT = 滤波器输出

A = 增益(跨导)

ZFILTER = 滤波网络阻抗

ΔT/T = “上”、“下”输入占空比

其中:

T1、T2、T3 = 与环路滤波元件有关的时间常数

式6为基本的环路传输函数。

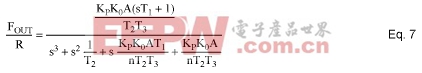

其中:

FOUT = 环路输出

R = 环路输入

n = 反馈环路分频比

K1 = 鉴相传输增益

K0 = VCO传输增益

A = 电荷泵增益

F(s) = 环路滤波器传输函数

s = jω

式7为环路锁定条件下完整的环路传输函数。

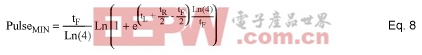

式8为避免死区效应的最小脉冲宽度近似值。

其中:

PulseMIN = 鉴相器输出要求的最小脉冲宽度

tF = 鉴相器输出下降时间(20%到80%)

tR = 鉴相器输出上升时间(20%到80%)

tL = 环路滤波最小输入脉冲宽度

式9给出了最大输入相位范围与工作频率和鉴相器时延的函数关系。

其中:

ΘMAX = 最大输入相位

tpRD = 从R输入到D输出的传输时延

F0 = 工作频率

- 小数分频与快锁芯片ADF4193的原理与应用(11-08)

- 全数字锁相环的设计及分析(03-01)

- 基于锁相环的频率合成电路设计(07-30)

- 锁相环中YTO自校准技术的应用(10-02)

- 基于DDS+PLL技术的频率合成器的设计(07-23)

- 锁相环在反馈电路上的应用(01-10)