F类功率放大器漏极电压研究

摘要 F类功率放大器实现高效率的基本原理,是利用输出滤波器控制漏极输出的电压或电流波形。基于这一点,文中首先理论分析了在不同谐波比例下的漏极电压波形,然后利用电磁仿真软件进行验证。结果表明,仅有三次谐波和基波组合在一起时,当三次谐波和基波电压比K=0.111时,漏极电压波形最平坦;当K接近0.4时,漏极电压波形趋于方波。最后选择合适的谐波比例,设计了一款功率附加效率最大值达到88.074%的F类功率放大器。

关键词 F类;功率放大器;漏极电压;功率附加效率

近年来,无论在全球移动通信系统、第三代移动通信系统、无线局域网等民用领域,还是在雷达、电子战、导航等军用领域,射频功率放大器作为这些系统中的前端器件,对其低耗、高效、体积小的要求迅速增加。

众所周知,功率放大器是射频电路众多模块中功率损耗最大的,作为系统的核心和前端部分,它的效率将直接影响系统效率,因此效率问题成为现代功率放大器的研究热点。在大多数功率放大器中,功率损耗的主要是晶体管损耗,主要由电压和电流产生的,从而提出开关类功率放大器,主要有D类,E类和F类。其中F类功率放大器专门设计一个谐波网络来实现漏极电压和电流波形控制。理论上,F类功率放大器的漏极效率为100%,被称为新一代功率放大器。

1 F功率类放大器的工作原理

传统功率放大器由于输出电路上的功率消耗,其工作效率很低。为增加传统功率放大器的工作效率,理想的F类功率放大器使用输出滤波器对晶体管输出电压或电流中的谐波成分进行控制,归整晶体管输出的电压和电流波形。从而实现集电极电流的角度参数为90°,即保持集电极波形为半个正弦波,集电极电压波形为方波,并且两者的相位差是λ/4,这样集电极电压和电流的波形就没有交叠区,从而达到100%的理想效率。

100%理想集电极效率的阻抗条件应是

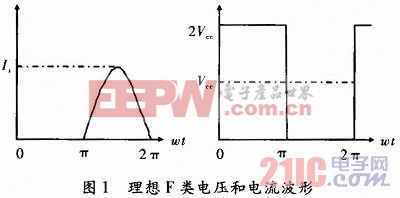

满足上述的阻抗条件实现的理想F类功率放大器的电压和电流波形如图1所示。

此时,如果驱动信号是一个占空比为50%的方波信号,晶体管可近似作为一个理想开关,晶体管输出的电压波形中包含各奇次谐波成分。流过开关的电流中仅包含有基频频率成分和各高阶偶次谐波成分。这样由奇次谐波的总和来近似方波的电压波形,基波和偶次谐波的总和来近似半正弦波的电流波形。从而得到电压和电流表达式如下

2 F类功率放大器的漏极电压分析

F类功率放大器设计的基本原理是控制晶体管漏极的谐波电压和电流信号,从而实现漏极电压为方波信号,电流为半正弦波信号,这也是实现高效率的根本原因。

然而,在现实设计中难以对所有谐波都进行控制的理想F类模式,增加考虑谐波的次数会在较大程度上增加设计的难度,并且效率的提高并不明显。在只考虑2次和3次谐波的情况下,最大效率可达81.7%。因此在分析中,只考虑3次以内的谐波。

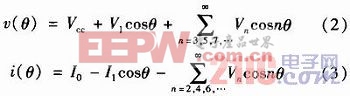

仅有3次谐波和基波组合在一起时,漏极电压如式(4)所示

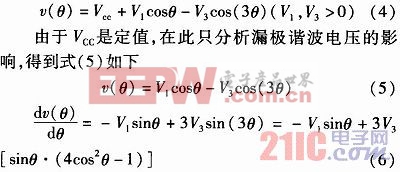

式(4)即为在只考虑3次谐波时,通过1,3次谐波的电压波形合成方波,若令K=V3/V1,下面分析不同K值下,如何由各次谐波信号合成方波。

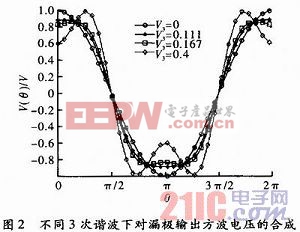

将V1归一化,利用Matlab做出上述理论分析3种情况下的曲线图,如图2所示。

由图2可以看出,在只考虑3次谐波的情况下,当K=0.111时,波形最平坦,与文献中所述3次谐波峰化时的最平坦波形理论一致。当K在(0,0.4)之间,小于但接近V1。当K接近0.4时,Vpk接近V1,趋向于方波。这就意味着即使不改变直流输入功率,不需要改变所有的漏极电压,只改变K值也可以改变电路输出,从而影响整体的性能。这样就可以通过改变K值,改变电压和电流曲线,提高整个电路的输出功率和效率,这也是F类结构的本质。

为了更好地验证上述理论,使用电磁仿真软件,调整不同的负载网络,实现K值分别为0.111、0.196和0.328的漏极电压波形,结果如图3所示。

图3是将一次谐波输出电压V1归一化后得到的仿真结果,图中标示的m1、m2、m3分别是归一化后的漏极输出各次谐波电压峰值。从图中可以看到,在3次谐波输出电压V3分别为0.111、0.196和0.328时,由漏极输出1次和3次谐波合成的电压Vd都V1。

其中,当K=0.111时,Vd的峰值是0.889,和理论上的K=0.111时Vpk=0.889V1一致,而且波形最平坦;当K=0.328接近理论分析中的0.4时,Vd=0.987接近V1,波形同样趋向于方波。可以看出,所有的仿真结果和理论基本一致。

3 设计实例

采用Cree公司10 W的GaN HEMT CGH40010,Rogers公司的RT5870基板,基板材料Er=2.33,基板厚度为0.79 mm,基频1 GHz,工作偏置点选为Vds=28V,Vgs=-2.5V。

在此次设计中,改变传统的F类功率放大器只考虑输出谐波的控制,同时考虑输入谐波控制网络的设计。

输入和输出2、3次谐波控制网络如图4所示。

- 采用异相功率放大器提高WLAN系统功率效率(01-22)

- 什么是高功率放大器(01-24)

- 功率放大器的使用极限(01-26)

- 封装了硅晶体管裸片的S波段功率放大器(上)(03-01)

- 如何利用实用的方法构建C类功率放大器(下)(05-18)

- 如何利用实用的方法构建C类功率放大器(上)(05-18)