基于FPGA的数字示波器设计

div,100 mV/div和10 V/div,即每div可代表1 000 mV,100 mV和10 mV。

A/D转换模块的模拟信号输入端的输入信号电压为0~2 V,当示波器满刻度显示时,被测信号的幅度将分别为:V11=1 V/div×10 div=10 V,V12=0.1 V/div×10 div=1 V,V13=10 mv/div×10 div=100 mV。A/D转换器的满刻度输入值为Vmax=2 V,程控放大器电路的增益AN=Vmax/VIn,其中N=1,2,3,对应于3档不同垂直灵敏度的增益分别为:A1=2/10=0.2;A2=2/1=2;A3=2/0.1=20。

A/D转换器的满刻度输入值为Vmax=5 V《10 V,将AD采样的值和数字信号的值据当前档位进行计数存储,即1μs/div时每10个点保存一个,1 ms,/div时每10 000个点保存一个,1 s/div时每采样10 000 000个点保存一个。

3.4.2 扫描速率分析

A/D的转换速率取决于被测信号的频率范围,或DSO对扫描速度的要求,设计扫描速度含1 ms/div,1μs,/div,1 s/div三档,通过FPGA内部建立分频电路实现了最高采样率16 MS/s,每10倍频步进,共六档,增加了该示波器的实用性。水平显示分辨率为64点/div,以保证显示波形清晰稳定。

3.5 VGA显示部分

VGA显示模块使用双缓冲机制,软核MicroBlaze通过读写显存来控制VGA显示。VGA显示可显示3种颜色,利用了SOPC的优势。GRAM位宽32b,大大提高了FPGA刷屏的速度。vga_dn与GRAM对内嵌的MCU设计成为BlackBox,MCU只需向相应地址发送合适数据即可显示想要的波形。本设计主要实现了的显示为:底色,汉字,示波器的显示框,波形数据。通过取字摸的方式,可在显示屏上显示中文信息。当部分的数据进行综合时,这几部分的数据各自有不同的优先级,当多部分重叠时,根据优先级显示出来。

4 总体效果

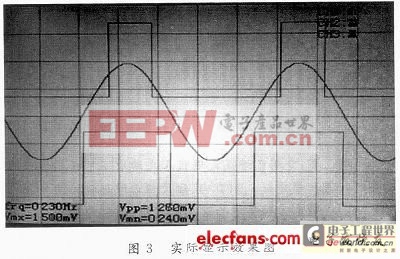

图3为同时显示2个数字通道和1个模拟通道的界面,通道1(CH1)为模拟通道,通道2(CH2)和通道3(CH3)为数字通道,输入信号为一正弦波,峰一峰值为1.2 V,通道2,设定输入信号信号电压大于0为高电平,反之为低电平,故通道2为占空比为50%的矩形波。通道3设定输入信号大于3.3 V为高电平,反之为低电平,故在本图上通道3为占空比约为25%的矩形波。由图可知观察值与计算值相符。

5 结语

设计实现了一款基于FPGA的VGA显示的多通道数字存储示波器。FPGA的高速性比其他控制芯片更适合于高速数据的采集和处理,另外FPGA内部存储模块在完成输入信号的量化存储速度上有着外接RAM无法比拟的优势。通过测试,设计系统比较好地完成了各项设计要求。

- 电源管理总线的结构与优势(11-19)

- 新型灌封式6A至12A DC-DC μModule稳压器系列(11-19)

- 低电压PLD/FPGA的供电设计(01-24)

- 基于FPGA的高精度数字电源(02-12)

- 功率分配系统(PDS)设计:利用旁路电容/去耦电容(04-29)

- 具有多个电压轨的FPGA和DSP电源设计实例(05-22)