一种双相位锁相放大电路设计

摘要 为更好地提取被噪声淹没的微弱信号,在分析了锁相放大器原理的基础上,采用CD4046和AD630设计了一个双相位锁相放大器,并进行了实验验证,实验验证结果表明,该放大器可以测量1 mA以下的交流电流,灵敏度为20 mV/mA,精度0.05%,是一种高精度、实用型锁相放大电路。

关键词 锁相放大电路;CD4046;AD630

随着科技的不断进步,被噪声掩盖的各种微弱信号的检测越来越受到重视,常用的检测方法有同步累加和锁相放大法。文中主要论述一种实用的锁定放大器的设计方法。

1 锁相放大原理

1.1 锁相放大原理及双相位锁相放大器

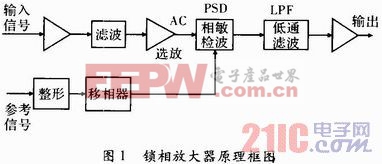

锁相放大器的工作原理结构如图1所示,包括想信号通道,参考通道,相敏检测器(PSI))和低通滤波器(LPF)。

信号通道对调制正弦信号输入进行交流放大,将微弱信号放大到足以推动相敏检测工作的电平,并且要滤除部分干扰和噪声。图中滤波电路选择带通滤波电路,经过带通滤波电路后的信号输入信号与参考输入信号进入PSD做一个乘法。PSD的功能是将输入信号与参考信号进行混频,输出和频信号和差频信号。LPF用于输出相乘后的差频信号,同时滤掉和频信号,从而得到放大后的微弱信号。参考可以是从外部输入的某种周期信号,也可以是系统内原先用于调制的载波信号或者用于斩波的信号。在外差式震荡技术中被称作本地振荡,用于做乘法运算实现的信号,在锁相放大器中被称作参考信号是从外部输入的。

频率变换是通过乘法运算实现的,一般的乘法运算模拟电路,其线性度和稳定性均有问题,因此,在实际的锁相放大器中,频率变换是采用开关元件进行同步检波来实现。由开关元件所进行的同步检波电路,称作相敏检波器,相敏检波器是锁相放大器的核心。

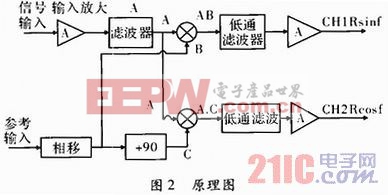

PSD的输出信号会因为输出信号和参考信号而产生较大变化,因此导致LPF的输出也会变化,即锁相放大器的测量值会发生变化。对于单相位锁相放大器,除了相位差为0之外,在其它相位差情况下,不能很好地测量被测型号的大小,所以此时应该将参考信号的相位移动90°,试用两个PSD,组成双相位锁相放大器,这样就能正确的测量振幅和相位,其原理如图2所示。

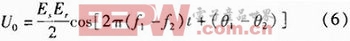

被测信号经过放大滤波后分别与两个正交的参数信号相乘,再经过低通滤波后得到的是直流分量,直流分量经过放大后输出,被测信号的幅值与R的关系为

通过式(1)可以测量被测信号的幅值。其中φ为被测信号与参考信号的相位差。正交参考信号的产生是通过集成锁相环实现。

1.2 锁相放大电路中的相关器原理

锁相放大电路中最重要的部分是相关器(PSD)部分,它是锁相放大电路的核心,起着至关重要的作用。相关器是相关函数的物理模型,是一种完成被测信号和参考信号互相关函数运算的电子线路,相关器又叫相敏检波器。

设输入信号

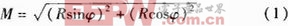

上式表明,相敏检波器的输出包括两部分,前者为输入信号与参考信号的差频分量,后者为和频分量。当被测信号与参考信号同步时,即f1=f2时,差频分量为零,这时差频分量编程相敏直流电压分量,而和频分量为倍频。其物理意义表示信号经过相敏检波以后,信号频谱相对频率做了相对位移,即由原来以f1为中心的频谱迁移至以直流和倍频为中心的两个频谱,经过低通滤波滤除倍频分量,从而使输出变为

因为f1=f2,设θ=θ1-θ2,则最后经过低通滤波后只有直流分量能通过,其它与时间t有关的项不能通过低通滤波,所以经过想敏检的输出信号经过低通滤波后只剩直流分量 。

。

2 双相位锁相放大器的设计

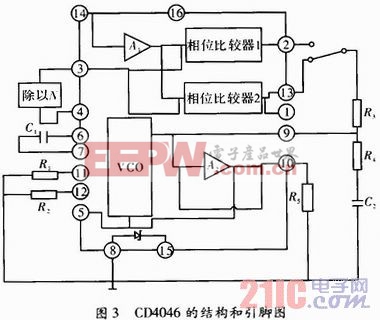

根据以上理论分析:采用集成锁相环CD4046来产生所需要的正交参考信号和AD630作为PSD电路来设计该电路。锁相环是一种反馈控制电路,其目的是消除频率误差。CD4046内部结构及引脚如图3所示,CD4046有两个相位比较器,比较器1采用异或门结构,当两个输入信号的电平状态相同时,比较器输出为低电平,比较器1输出的信号频率是信号输出频率的两倍,并且与两输入信号之间的中心频率保持90°相移,其所输出的波形不一定对称,其要求两输入信号之间的占空比为50%,此时锁定范围最大,相位比较器2是一个上升的数字存储网络,对输入信号的占空比要求不高,允许输入非对称波形,但其具有很宽的捕捉频率范围。基于此设计U1和U2采用相位比较器1输出,使输出的波形为占空比50%,从而得到最大的锁定范围,U3的输入信号相位相对于U1平移了90°,U2和U4使用相位比较器2,使信号具有很宽的频率捕捉范围。此部分的难点在于CD4046中振荡电路参数的确定。

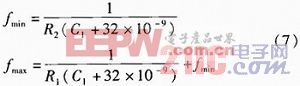

参数的确定参考文献可知:环路参数的计算主要是确定与VCO输出频率有关的电阻R1和R2,电容C1的值以及环路滤波参数的值,即R3和R4。由参考文献得振荡电路各参数如下

其中,10 kΩ≤R1≤1 MΩ;10 kΩ≤R2≤1 MΩ;100 pF≤C1≤0.01μF。

环路滤波参数的计算:利用参考文献的结论可知,鉴相器灵敏度 ,Vcc为供电电源。压控振荡器的灵敏度

,Vcc为供电电源。压控振荡器的灵敏度

其中fr为输入信号频率,本设计选取η=1,fr=1 500 Hz,C1=0.01 μF,C2=10μF则可推出R1=R2=1 MΩ,R3=112 Ω,R4=212 Ω;总体电路如图4所示。

其中fr为输入信号频率,本设计选取η=1,fr=1 500 Hz,C1=0.01 μF,C2=10μF则可推出R1=R2=1 MΩ,R3=112 Ω,R4=212 Ω;总体电路如图4所示。

- 一种双相位锁相放大电路设计(10-16)

- 同步降压转换器电路设计基础(01-01)

- 电路设计基础知识--变压器(01-29)

- 不连续模式反激变换器的基本原理和电路设计(01-05)

- 牛奶成份检测仪光强检测电路设计原理(11-05)

- WCDMA分布式基站低噪声放大器电路设计(09-12)