采样时钟抖动对ADC信噪比的影响及抖动时钟电路

时间:05-24

来源:互联网

点击:

动为:

如果使用的ADC为AD9245,参照图1可以看出:当ADC前端输入信号频率低于50MHz时,AD9245的信噪比将优于65dB,输入信号频率低于100MHz时,AD9245的信噪比将优于60dB。

基于极低相位噪声温度补偿晶振的非可变采样时钟

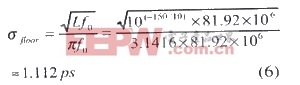

在确定采样频率后,如果并不要求时钟产生电路产生的时钟可变的话,就可采用基于温度补偿晶振的时钟产生方法。首先由公式(2)根据所需的ADC信噪比确定最大容许的时钟抖动,然后由公式(5)反推出最大容忍的相位噪声基底,最后给出不同频率偏差点上的相位噪声特性并交由晶振制作工厂定制即可。这是一种最简单的时种产生方法,基本不需要作太多调试,但它只适合固定时钟采样的情况。

在利用上述两种方法产生采样时钟时,一个值得注意的地方就是采样时钟电路应尽可能与存在噪声的数字系统独立开来,在采样时钟的通路中也不应该有逻辑门电路,一般来说,一个逻辑门将会产生几个皮秒甚至十几皮秒的定时抖动。在设计时应该把采样时钟产生电路和系统的数字及模拟部分分离。

结语

本文首先分析了采样时钟抖动对ADC信噪比性能的影响,然后指出产生时种抖动的原因,最后给出了两种实用的采样时钟产生方案:基于低相位噪声VCO的可变采样时钟及基于极低相位噪声温度补偿晶振的非可变采样时钟的产生方法。

- 使用JESD204B同步多个ADC(04-29)

- Giga ADC 介绍及杂散分析(下)(01-22)

- 高速ADC时钟抖动及其影响的研究(05-31)

- 连续时间Sigma-Delta模/数转换器(下)(06-17)

- 12位串行A/D转换器MAX187的应用(10-06)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)