Giga ADC 介绍及杂散分析(下)

3、Giga ADC杂散的分析

ADC应用中,输出的杂散信号决定了ADC的动态范围。在传统的流水线ADC中,起决定作用的主要是谐波杂散,即输入信号的二次、三次或更高次谐波混叠进入第一个Nyquist区。除此以外,GigaADC的interleave架构带来了其它杂散。如前文说提到的,为了达到更高的采样速率,每路ADC实际包括两个子ADC,这两个子ADC工作在interleave模式下。在这种情况下,两路子ADC之间的失配将会产生新的杂散信号。总体来说,Giga ADC的杂散主要分为三类杂散信号:1)interleave杂散;2)固定频点杂散;3)和输入信号相关的杂散。

3.1 Interleave相关的杂散

Interleave模式,如Figure7所示,就是相同的输入信号,输入到两个(或N个)采样率相同,但采样时钟相位相反(或相差2π/N)的ADC中,从而达到采样率增倍的目的。但由于两路ADC不可能完全一致,存在一些失配,从而导致了一些输出杂散的生成。这些失配包括偏置误差、增益误差以及采样时钟的相位误差。

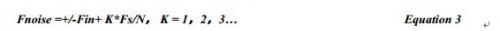

这里假定:N:一路ADC中包含的子ADC个数Fin:输入有用信号Fnoise:输出的杂散信号Fs:ADC采样时钟

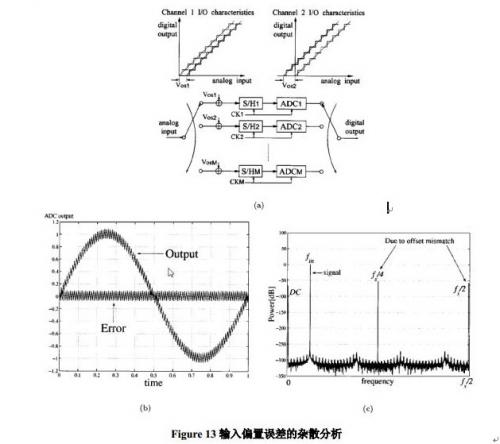

3.1.1输入偏置误差

假定ADC其它参数都是理想的,只考虑输入偏置误差。通过数学分析可以得到,输入偏置误差带来的杂散主要分布在

从Figure13可以看出,输入偏置误差带来的杂散和输入信号的幅度和频率没有关系,从频域上看,均匀的分布在第一Nyquist区。由输入偏置带来的杂散固定的分布在公式一给出的各个频点。

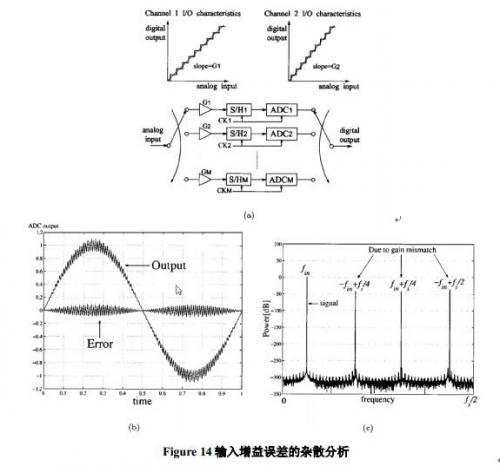

3.1.2输入增益误差

假定输入电路除增益误差以外,其它参数都是理想的,可以看出当输入信号幅度增大时,增益误差也随之变大。输出的误差信号类似于输入信号的一个调幅输出,可以得到,增益误差导致的杂散信号出现位置如下:

从分析可以看出,由于增益误差导致的输出杂散幅度和输入信号的频率无关,但和输入信号的幅度有关,输入信号幅度变大时,杂散幅度增加;反之亦然。

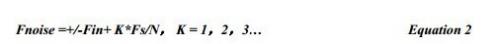

3.1.3采样时钟的相位误差

如果两个或多个采样时钟之间存在相位误差(skew),同样会带来杂散。由于相位误差带来的误差最大出现在输入信号压摆率最大的地方,即过零点,即这类杂散类似于输入信号的调频输出。杂散信号出现的位置在:

采样时钟的相位误差和输入增益误差带来的杂散位置相同,但相位误差输出的杂散和输入频率有关,当输入频率越高,误差越大;而偏置误差和增益误差带来的杂散和输入频率无关。

3.2固定频点杂散

相对于interleave杂散,固定频点杂散和输入信号的频点无关,主要取决与系统时钟,ADC及子ADC的采样时钟,数据输出的随路时钟以及系统中其他时钟源的耦合干扰。固定频点杂散因为位置固定,应用中很容易预判这些杂散,从而在系统设计中规避这些杂散存在的频点。

3.2.1采样时钟杂散

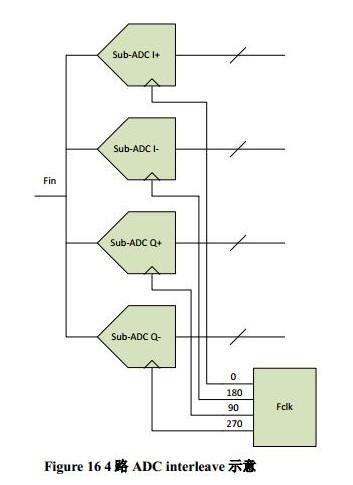

如Figure 16所示,当四个ADC工作在interleave模式下,四个ADC的采样率都是Fclk,但相位相差90度,这样整个ADC通道的实际采样率为4*Fclk;输出的频谱中,在Fclk频点处有一个固定的采样时钟杂散。这个主要是时钟的泄露,采样时钟从芯片内部或板上耦合到数据的输出。

3.2.2数据输出的随路时钟

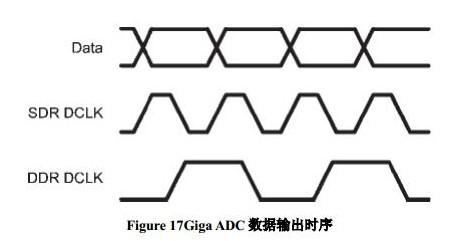

在Giga ADC中,数据的输出是并行LVDS总线;同时这些总线可以1:2 Demux或者Non-demux;在Non-demux,数据速率和采样速率是一致的;在Demux模式下,数据速率降低一倍,但数据总线增加一倍。同时,Giga ADC数据输出的随路时钟可以是DDR或SDR,如下图所示。在Demux和DDR同时使能的情况下,随路时钟DCLK只是采样时钟的1/4,这个时钟杂散可能出现在Fs/4的地方。

3.3和输入相关的杂散

前面提到,和输入相关的杂散主要是输入信号的奇偶次谐波混叠进入ADC的第一Nyquist区。这类杂散主要通过外部的抗混叠滤波器加以滤除以及信号输入端的匹配,差分两端的平衡来优化。这类杂散在传统的ADC中已经讨论很多,这里就不再赘述。

3.4杂散信号的优化

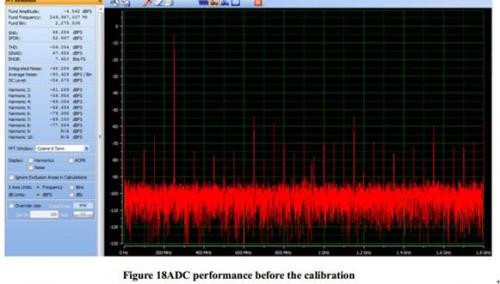

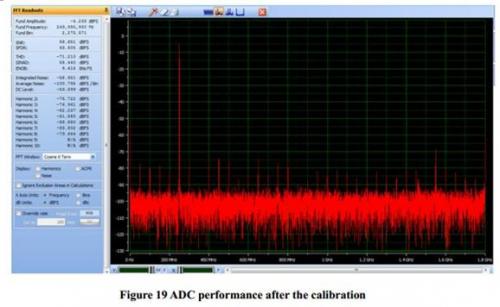

为了达到最佳的输出杂散性能,在Giga ADC,主要采用了校准环路,来优化输入电路的偏置误差、增益误差。如下图所示,在校准前后,ADC的性能可以优化10dBc以上。

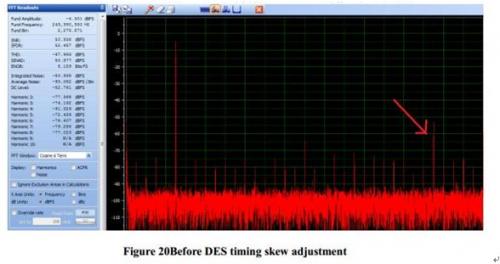

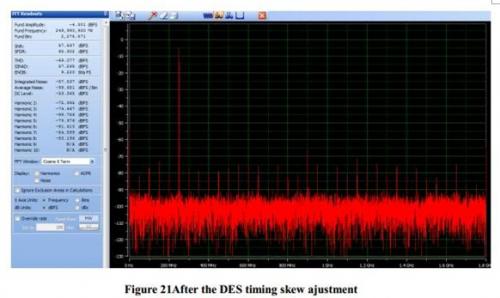

同时,当Giga ADC工作在DES mode,两路采样时钟间的skew对于Fs/2- fin的杂散非常重要;芯片提供了两路采样时钟的skew调整功能,可以通过寄存器的配置来降低Fs/2 - fin的杂散,如下图所示。

除此之外,ADC的外部输入电路设计也需要尽量优化,确保两路差分电路的平衡一致,阻抗的匹配。Giga ADC提供了DESI,DESQ,DESIQ,DESCLKIQ等几种DES模式下输入结构;综合输入平坦度,插入损耗和最终的ADC性能测试结果,DESIQ模式的性能最佳,并且推荐采用多层Balun和以下的输入电路。

Giga ADC 杂散 增益误差 采样时钟 相位误差 相关文章:

- Giga ADC 介绍及杂散分析(上)(01-22)

- 12位串行A/D转换器MAX187的应用(10-06)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- 12位串行A/D转换器的原理及应用开发(10-09)

- 在射击探测器中增加口径确定功能的简单电路(11-13)

- 一种折叠共源共栅运算放大器的设计(11-20)