存在串扰时的抖动和定时分析

串行数据标准持续迅猛发展,大幅度改善了PC和服务器系统的性能。测试这些更高速的标准、找到抖动证据,对长期稳定性及在设计中实现优异的误码率(BER)目标至关重要。为高效进行分析,首先要选择适当的仪器,很好地了解仪器噪声、上升时间及三阶谐波性能、四阶谐波性能、五阶谐波性能等因素。

但还不仅仅是测量这么简单,合适的仪器必需与适当的分析工具配套使用。在测试8 Gb/s以上的串行数据速率时,还要考虑其它因素,如抖动分离和去嵌/嵌入。在本文中,我们将重点介绍存在串扰时的一种新的抖动分离方法,随着通路数量提高,以提升计算系统吞吐量,串扰问题正越来越多。

所有采用电压跳变表示定时信息的电气系统都有定时抖动。在历史上,电气系统通过采用相对较低的信令速率来减缓定时抖动(或简称为抖动)的负面影响。随着数据速率攀升到8 Gb/sec以上,抖动占信令间隔的比重已经很大,了解抖动类型和抖动来源对成功部署高速串行技术非常关键。

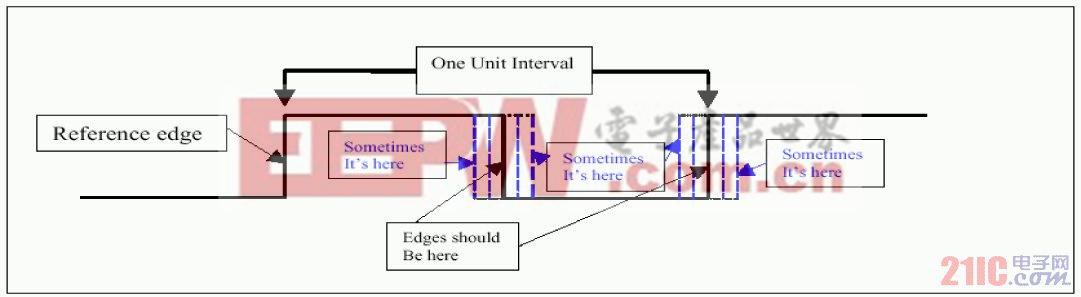

简单地说,抖动是边沿与本应位置相比的偏差,如图1所示。根据ITU的定义,抖动 是数字信号在有效时点较理想时间位置的短期变化.

图1 抖动是边沿较本应位置的偏差

可以通过多种方式测量单个波形上的抖动,包括周期性抖动、周期间抖动和时间间隔误差(TIE),设计通常决定着哪种指标合适。在独立式振荡器中,信号是时钟,可能会跳频或扫频。这里,周期性抖动是合适的指标。在串行数据流的发射机中,信号是数据流,ISI(码间干扰)是关键问题。这里,TIE抖动是合适的指标。

处理抖动问题的工程师有大量的仪器可以选择,每种仪器都有独特的优势和劣势:

· 实时数字存储示波器(DSO)恢复整个波形,可以测量任何指标,可以用于TIE、周期到周期抖动和周期性抖动测量。但它在频率(或位速率)、解析频谱、小的抖动及多电平调制方面有局限性 .

· BER测试仪(BERT)特别适合TIE抖动,特别是TJ或总抖动,这是TIE的一种形式。BERT的优势是它计数每个比特,但测试执行起来耗费时间较长。

· 实时频谱分析仪(RTSA)可以用于周期间抖动测量和周期性抖动测量,支持移动设备的复杂调制,查看时钟、PLL,了解其动态性能。其局限性包括跨度(低于100 MHz)和带宽信号,具有大的调制频谱。

· 等效时间采样示波器提供了最佳的带宽,可以用于串行数据的所有抖动测量。目前,这些示波器是唯一支持噪声分析和BER眼图的仪器。其局限性是没有实时捕获功能,只能用于重复的码型,某些抖动频谱有假信号。

人们经常提出的一个问题是如果我们最终只关心BER,那么为什么还要担心抖动。这是因为眼图(宽度)闭上得太多时会导致误差。抖动和噪声分析工具可以迅速预测和分析BER中的问题。最终,一切都归结于误差,而消除设计中的这些误差要求了解抖动过高的一个或多个原因。

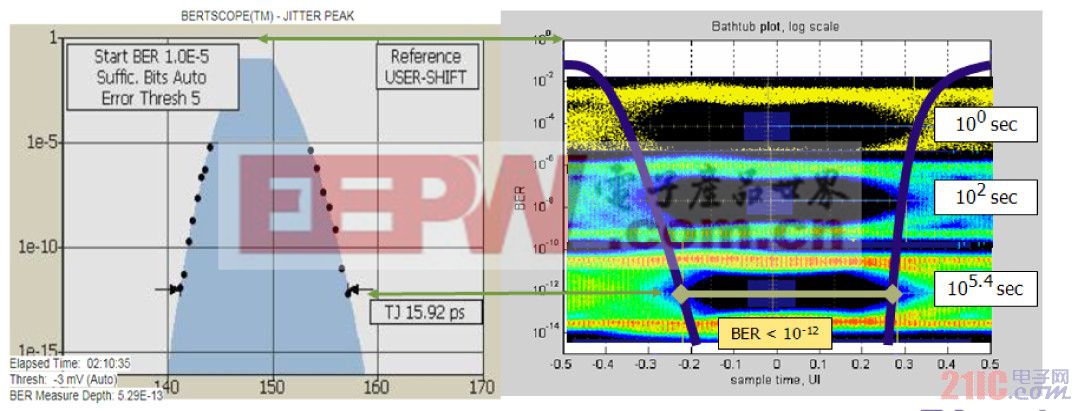

首先应从整体BER角度了解系统的运行方式。示波器使用眼图和统计分析,生成浴缸图。之所以叫浴缸图,是因为在极限变化时,得到的图形形状像浴缸。在使用BERT仪器时,每个位的具体数量会得到一个抖动峰值图。如图2所示,左面来自BERT的抖动峰值与右面示波器抖动浴缸图几乎完全等效。

图2 左面BERT 抖动峰值与右面示波器抖动浴缸之间的BER性能等效图

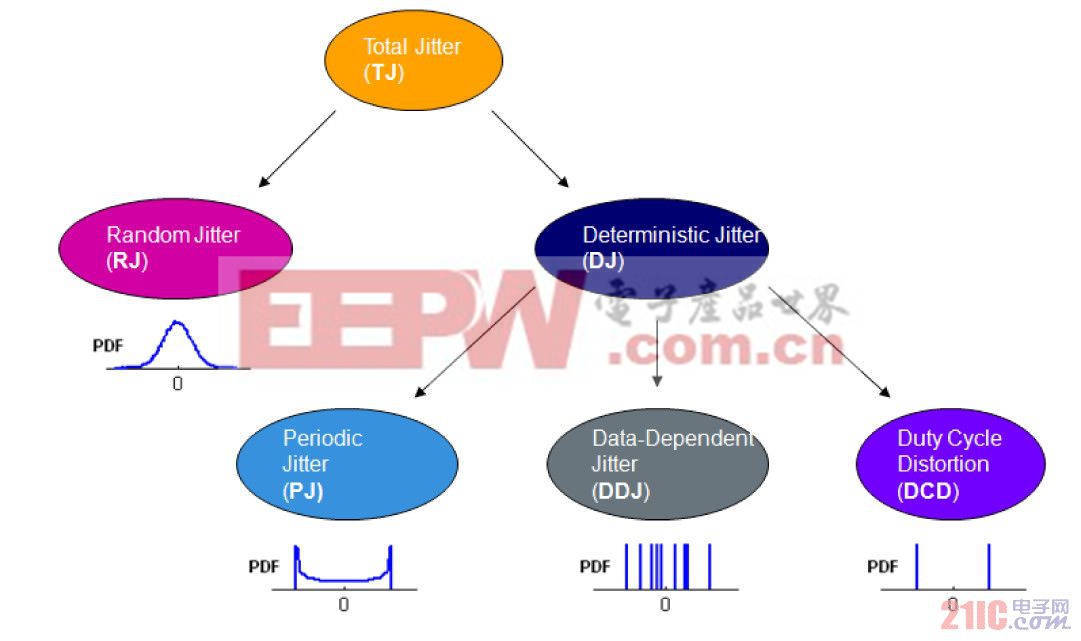

鉴于结果紧密对准,示波器成为BERT非常实用的补充,因为使用BERT测量直到BER=10-12的TJ会需要几个小时的时间,结果并不能揭示哪类问题导致抖动。示波器可以以智能方式测量少量数据,然后把抖动划分成各种抖动成分,其一般采用图3所示的公认的抖动模型。通过做出假设,示波器可以进行

图3 业内抖动模型:2001-2010

串扰问题为实现性能目标,大多数串行系统采用多条通路。随着频率和数据速率提高到10 Gb/s以上,少量的串扰就会吃光抖动预算,产生定时问题。

在一个信号受到相邻信号影响时,会发生串扰。在数据速率很高时,信号传播方式更像是导波,而不是简单的DC电流。波由传导轨迹引导,但通过介电介质辐射,一般是FR4.当存在一个以上的信号时,电路板上的每条传导轨迹在其它每条轨迹上带有假信号。公认的术语是侵入信号会在被侵入信号上导致串扰。在引导被侵入信号的导体捡拾到侵入信号时,就会发生串扰。电路布线中不可避免的不连续点(如连接器和通路)是关键点,在生成串扰时,它们的行为方式类似于天线。

实时采样示波器和等效时间采样示波器采用基于频谱的抖动分析技术,隔离各种抖动成分。在实时采样设备上,如果频率成分没有假信号,那么抖动和电压噪声频谱有副谐波峰值,它们会被涂抹到电路板谐振形状中,而不是表现为锐线。在采样不足的

- RJ45双绞线水晶头的制作(04-26)

- 24位低功耗模拟前端-ADS131E08 解决方案(07-29)

- 指状电源和地线之间的串扰(08-04)

- 完整地平面的串扰分析(06-22)

- 平行交叉地平面的串扰(06-26)

- 开槽地平面的串扰(06-26)