开槽地平面的串扰

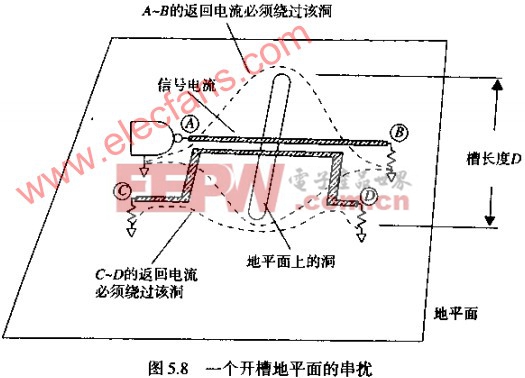

图5.8中描述的串扰情况是一个典型的布局设计中错误,称为地槽。当一个布线设计工程师把正常的布线层的究竟用尽,想在地层面上塞进一根走线时,会出现地槽。通常采用的方法是地层面上分割出一个长条,然后在里面布线。对于垂直经过该槽的走线,地槽会增加其电感,也增加了串扰。这种做法应该是被禁止的。

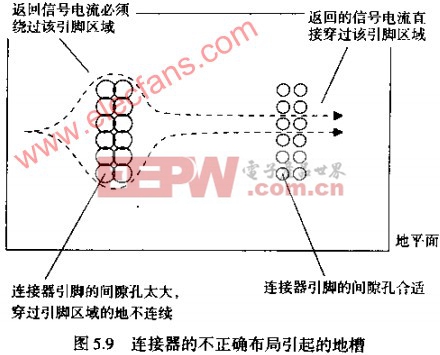

在密集的背板上经过连接器的区域时也会发生地槽的情况,因此应该确认每个引脚的间隙孔,保证所有的引脚之间的地保持连续(见图5.9)。

如图5.8所示,从驱动器A点返回的电流不能直接从走线A~B之下流过,而是转向绕过地槽的顶端。

经过转向的电流形成了一个大的环路,严重地增加了信号路径A~B的电感,从而减慢了在B点收到信号时的上升时间。

转向的电流周时与走线C~D的返回电流路径环路形成严重重叠。这个重叠在信号走线A~B和走线C~D之间引起一个大的互感。

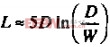

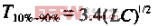

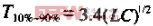

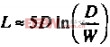

与走线A~B串联的有效电感是:

其中,L=电感,NH

D=槽长度,IN

W=走线宽度,IN

槽宽度几乎不影响信号走线的电感。任何宽度的一个槽,无论多窄,都会使电流转向,绕过槽的两端。槽的宽度从零一直到等于槽的长度,效果都一样。

如果走线由在靠近槽的一端,电感就比较少一些。如果槽长度和走线宽度接近或小于线宽,就几乎没有影响,如果槽靠近走线,但没有和走线交叠,影响也较小。

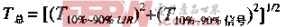

由槽导致电感的变化所引起的上升时间损失,其数值取决于所采用的端接情况。最坏的情况是一条长线,在电感两端的源端阻抗都是ZO。因此L/R滤波器的10~90%上升时间的结果形式如下:

使用平方求和再开平方根的方法合并这一上升时间和正常信号的上升时间:

对于驱动一个大的容性负载C的短线,其10~90%的上升时间为:

这样的一个电路可能会发生振铃。该电路的Q值取决于驱动器的源电阻RS:

当Q值大于1时,电路会振铃,当Q值接近1时,电路上的上升时间遵从式 当Q值小于1时,电路的上升时间比前式的时间慢。

当Q值小于1时,电路的上升时间比前式的时间慢。

如果第二条走线与第一条走线很近,也横穿了相同的槽,这两条走线将会紧耦合。第二条走线与第一条走线的耦合电感LM与式 中的L相同。

中的L相同。

如果第二条走线由在靠近槽的一端,它与第一条走线的耦合电感随着它与槽端的距离线性减少。

根据耦合电感和驱动电路的电流变化时间速率的知识,可以算出两条走线之间的交叉耦合电压:

对于一条长线,△I只是等于驱动电压除以特性阻抗:

对于驱动一个大的容性负载C的短线,电流变化速率是电压的二次导数:

文中第2式到第8式对于地平面中由任何阻断所引起的电感的分析都同样合适。

- 完整地平面的串扰分析(06-22)

- 平行交叉地平面的串扰(06-26)

- 完整地平面的串扰(06-26)

- RJ45双绞线水晶头的制作(04-26)

- 24位低功耗模拟前端-ADS131E08 解决方案(07-29)

- 指状电源和地线之间的串扰(08-04)