适用于HDTV应用的8位DAC

在一般的数/模转换器的设计中,译码结构通常采用分段结构。在一般的设计中,为了减少延时,通常使用锁存器,同时配合复杂电流源结构,这种结构通常需要较大的能耗,并且采样率不是足够高。为了得到更高的采样率和更好的线性度,在此基于TG结构,设计了单位电流单元矩阵和译码器电路,同时采用简单的电流单元电路设计。

1 结构选择

在此,采用电流舵型DAC设计。这是因为电压型DAC所需元器件多,开关层数也较多,一般用于低速转换器内;电荷型DAC随精度的升高,面积急剧增大,而且对寄生电容敏感;电流型DAC具有高速的优势,但不适用于低压电路。电流舵型DAC是对电流型DAC的改进,常用于分段电路中。

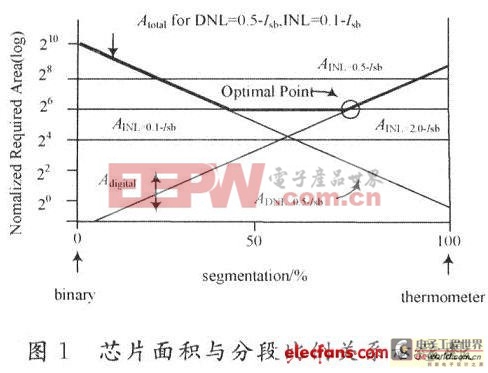

数/模转换器的译码方式一般分为二进制、温度计和分段式。温度计译码方式相对二进制译码方式,在减小DNL和INL方面有很大的优势,但是它的缺点是电路结构复杂。将二进制码和温度码结合起来,就产生了分段结构。在对匹配要求、高精度的高位采用温度计译码方式;低位采用二进制码方式,可以减少面积。这种分段结构既有二进制码结构简单的长处,又有温度码良好的线性特性。在这个设计中,提出使用电流源矩阵逻辑电路构成的高速8位DAC,根据Lin和Bult做了面积与分段比的关系图(见图1),为了在速度、分辨率、功耗、芯片面积、电路性能等多个方面得到一个折衷结果,分段的高6位采用温度计译码结构和低2位采用二进制译码结构。整个CS-DAC的结构如图2所示。

图2是一个说明8位分段式电流舵基本结构的例子。图中采用6+2分段结构,高6位数字信号通过行译码器(Rows Decoders)、列译码器(Columns Decod-ers)转换为温度计码,分别控制26-1=63个单位电流源,构成8×8电流源矩阵。多余的一个电流源作为Dummy器件,63个单位电流源和低2位二进制加权电流源的电流之和形成了阵列中整体电流源的电流。

2 译码逻辑电路

在DAC设计中,电流源单元、译码器和消除毛刺(噪声)结构是重要部分,DAC的性能由这些部分决定。为了改进在高频率动态线性,在此提出由传输门和晶体管组成组合逻辑译码电路。

2.1 传输门逻辑

因为NMOS管可以通过逻辑变量0传输,PMOS管可以通过逻辑变量1传输,用这两个MOS平行放置构成互补结构。在此,可以得到传输门(TG),并且对于TG,逻辑变量0,1都可以很好的传输。大家都知道,译码器之间的延迟时间是毛刺发生的主要原因,并且与全部使用CMOS逻辑电路比较,用TG设计的逻辑电路性能更好,延迟更小。经过验证,所有二输入逻辑门的可由传输门和反相器组成。作为一个事例,实现与非门逻辑,全部CMOS技术要求6只晶体管,但采用TG结构只需要5只晶体管。在内在DAC芯片上,它有两个信号,并且有翻转信号,因此没有反相器的需要,因而二只晶体管被减少。实验结果说明,芯片面积和功耗的大大减少了。

2.2 逻辑译码电路

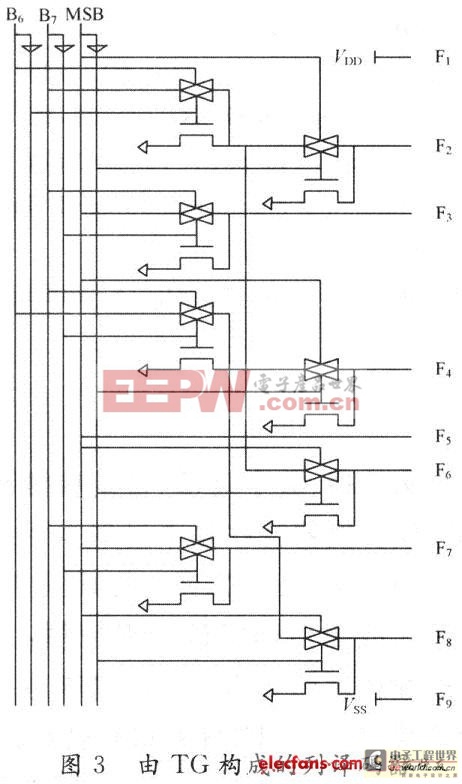

为减小功耗和减少延时,应该设计最少逻辑水平的行和列译码,运用TG逻辑电路组成3~8位行、列译码器。如此从高3位得到行译码器和从中间3位输入得到列译码器。运用TG的行译码器电路如图3所示。

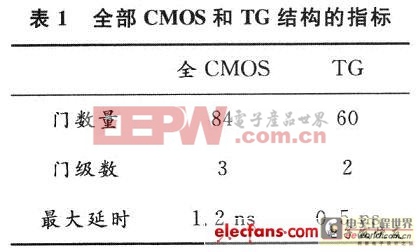

行译码器结构与列译码器基本相同,但没有电源节点。使用TG逻辑译码器的另一巨大好处是可以减少晶体管的数量。在静态逻辑,参考文献[9]的译码器由84 只晶体管组成,但用TG结构组成的行和列译码器有30只晶体管,并且总数是60。这意味着芯片面积可能也被减少。较少的晶体管级数也帮助减少延时。另一方面,使用TG结构的逻辑门最大级数可减少到2级;不使用传输门结构的全CMOS结构的最高门级数是3,以上充分说明使用TG结构更有利减少延时和改进工作频率。表1给出相关的参量对比。

2.3 工作原理

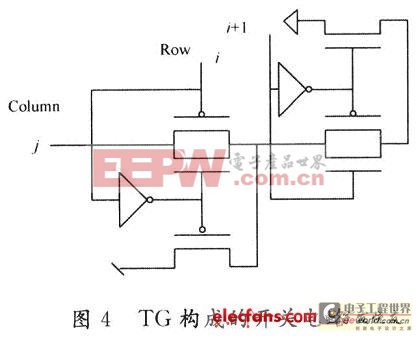

用行列译码器进行译码,单位电流源是导通还是截止,共有三种情况。第一种是所在行和下一行都是“1”,在这种情况下,无论列控制信号是否为“1”,该电流源均被选中。也就是说,对应的电流源开关状态为接通状态。第二种情况是所在的行控制信号为“1”,但是下一行的控制信号为“0”,这时,电流源是否被选中,要根据列控制信号来决定。如果列控制信号为“1”,则该电流源被选中;如果列控制信号为“0”,则该电流源不被选中,处于截止状态。第三种情况是所在行和下一行的控制信号均为“0”,那么不管其所在列的控制信号为多少,此电流源不会被选中,处于截止状态。TG构成的开关电路如图4所示。

3 电流源电路及减少毛刺电路

电流源电路是DAC的重要部分,同时为了减小毛刺反应,下面将介绍减少毛刺的电路。

3.1 电流单元

一般常用的设计均采用减少电路噪声和降低电流源的复杂结构。例如,差分电路、偏置电路、参考电流等需要很多数量的晶体管。在这个设计中,使用一个简单的电流单元结构,并且电流源采用由二只晶体管组成的电流源单元。与其他芯片相比,电路的面积可以大大减小,如图5所示。

- 模拟电路设计使HDTV体现出差异性(01-16)

- HDTV整合闭环架构与开环架构分析(08-25)

- 整合HDTV处理器和8VSB解调器的SupraHD 760处(11-07)

- Maxim推出用于LCD HDTV面板的多路输出电源芯片(10-31)

- HDMI设计指南:HDTV接收机应用中高速PCB的成功设计(04-19)

- 模拟电路设计使HDTV体现出差异性(01-02)