基于FPGA的DDC滤波器设计与仿真

上完成的。赛林思是全球领先的可编程逻辑完整解决方案的供应商,它研发、制造并销售范围广泛的高级集成电路、软件设计工具以及作为预定义系统级功能的IP(InteIlectual Property)核,客户使用Xilinx及其合作伙伴的自动化软件工具和IP核对器件进行编程。System generator是Xilinx公司进行数字信号处理开发的一种设计工具,它通过将Xilinx开发的一些模块嵌入到MATLAB的Simulink库中,可以在Simulink中进行定点的仿真,可以设置定点信号的类型,这样就可以比较定点仿真与浮点仿真的区别。并且它还可以生成HDL文件,或者网表直接供ISE调用。较之于直接用MATLAB进行算法的仿真其主要优势作于它是基于定点的,同时,它是由各个供应厂商直接提供的库,因此它能够充分认识FPGA内部的资源等,其仿真也 更精确可靠。

虽然,system generator能直接生成供底层FPGA调用的代码以及网表,但是,通常并不这样做。相对于人工编写的代码,system genera tor生成的代码相对冗余度高,资源利用也不及人工编写的代码合理。但是,在某些需要快速进行算法开发的项目中,这种方式无疑为用FPGA从事快速的算法开发提供了一个捷径。

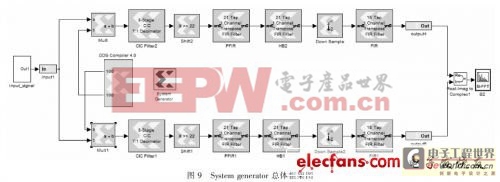

将MATLAB与system generator集成后,由图1所示的原理框图,搭建了用于仿真的system generator模块,如图9所示。

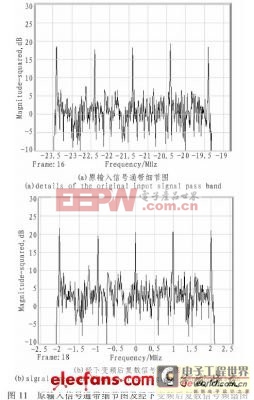

在输入端输入幅频响如下图所示的信号,其有用信号范围173~25.5 MHz。另外为了方便仿真结果的观察,又加入了2个大的噪声信号分别位于32.4MHz,12.4 MHz。

将上图所示的信号送入DDC网络后,信号变成I/Q两路信号,将这两路信号组合成复数信号后得到的复数信号的频谱图如图11(a)所示。

图11(a)为原输入信号的有用信号附近的细节图,而图11(b)为经过DDC网络后得到的复数信号的幅频响应图。由于simulink的频谱绘制工具显示刷新的问题它们看起来有了一点点的误筹,但是,也可以发现经下变频后的信号有效的恢复了原信号的频谱信息。它将原输入信号的负边频线性搬移到了以0频为中心的带宽为4.1MHz的频谱上来。

6 结束语

实际项目中接触到的信号处理任务大多为带通信号,如果直接采用传统的奈奎斯特采样定理对模拟信号进行采样,然后进行数字信号处理任务,这样对后端的DSP器件的实时性要求太高。因此,通常我们都要先用一个FPGA来完成数字信号的下变频操作,之后再由后端的DSP器件来完成信号处理任务。因此,如何合理的设计DDC下变频就显得特别重要。本文针对如何设计DDC滤波器以及基于FPGA的System Generator的仿真都作了简单的介绍。

- 电源管理总线的结构与优势(11-19)

- 新型灌封式6A至12A DC-DC μModule稳压器系列(11-19)

- 低电压PLD/FPGA的供电设计(01-24)

- 基于FPGA的高精度数字电源(02-12)

- 功率分配系统(PDS)设计:利用旁路电容/去耦电容(04-29)

- 具有多个电压轨的FPGA和DSP电源设计实例(05-22)