何时应对宽能带隙材料时代

首先来看看碳化硅。关于碳化硅功率器件的开发已经持续了20多年了。600V肖特基二极管作为第一款商用功率器件出现在10年前,而后逐步发展成结势垒混合PiN的肖特基二极管。碳化硅器件的好处在于其材料的耐用性。热传导性较硅器件提升三倍,同质性的基底和外延层允许垂直功率器件在硅片上均匀地散热,可以耐受大浪涌电流、高瞬态电压和高功率。

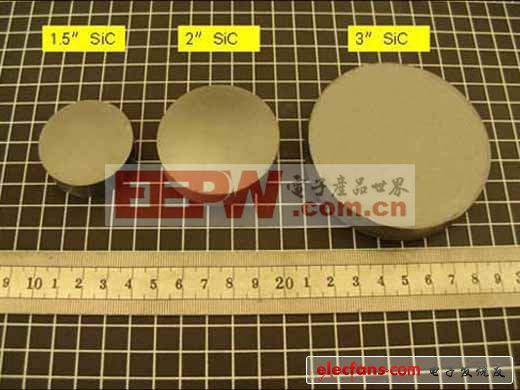

碳化硅晶片

现今,碳化硅晶体管开关正在进行最初的商业化,早期的MOSFET具有相对较高的导通阻抗,并且由于表面沟道活动性和栅极电介质应力而仍然而有其局限性。 新型MOSFET正处于开发之中,并可部分克服这些局限性。双极和JFET器件避免了这些问题,因此具有接近理论极限的更低阻抗。双极器件通常处于关断状 态,这在大多数应用中是必需的。新型BJT具有无存储时间、20ns开关时间、100以上的大电流增益、大电流下无增益下降、有益于稳定的负增益和Vcesat温度系数,并且无二次击穿等特性。虽然可以制造JFET在零栅极偏置电压下完成夹断,但这也增大了导通状态的电压,也将栅极电压的摆幅限制在3V以内。通 常导通的JFET的传导损耗几乎与双极器件持平,但是一般要求以串联方式将器件联成共发共基放大器(cascode),或者在允许“常开”工作的情况下至 少是负驱动。

氮化镓器件又如何呢?30V至200V的更低电压器件已经面市。在100V以下时,这种器件实际上具有比硅器件更高的导通阻抗。栅极电荷方面的少许优势是这些器件所具有的唯一先进之处,而在没有栅穿效应的情况下驱动器件会成为挑战。即将推出商用600V器件。这些器件中有一些是在碳化硅基层衬底上构建的,但是由于成本原因,大多数公司倾向于采取在硅基层上制作GaN外延的方式。由于存在广泛的晶体失配现象,这无疑成为严峻的工艺挑战;MOCVD工艺正处于开发之中,该工艺能够使层厚达到数微米,足够满足处理600V电压的要求,而没有过度的翘曲和变形。由于失配引起的不可避免的断层通常在109/cm2的范围内,需要给予抑制,以避免导电硅基层的泄漏,重要的是在薄膜中加入特别的杂质,以控制泄漏电流以及以及体电荷陷落。表面电荷和体电荷的陷落会引起导通电压的增加以及阻断电压的不稳定。幸运的是,最近报道在解决这些不稳定性方面已经取得了很大的进步。

氮化镓器件

从理论上讲,氮化镓垂直器件在传导率方面优于碳化硅器件。这一点常用明确的Rdson对比额定BV图形来表示。问题在于缺乏具有合 理的成本和直径的均匀的氮化镓基层。因此,几乎所有的努力都放在了横向高电子迁移率晶体管(HEMT)上面,这些晶体管并未延续垂直器件的思路。这些器件 的性能取决于减小特征尺寸、2维电子气(2DEG)接触阻抗以及漏极漂移长度。这意味要获取低阻抗,高表面电场是不可避免的,并且这些器件不能承受很大的 雪崩电流。这些器件必须采取保守设计的方式,以确保瞬变电压值不会达到实际器件的击穿电压。高电子迁移率晶体管是带有漏肖特基栅极的常开器件,所以,对于 高电压一般采用一种绝缘栅极结构和常闭器件设计中的一种创新方法。

碳化硅器件成功的关键是加快了解成本和材料缺陷方面的知识,开发基底和外延生产能力,并转换至150mm晶圆尺寸,以便使用广泛的晶圆生产能力。预计在今 后2至3年将会出现600V至1700V以及电压更高的商用器件。氮化镓器件成功的关键在于提高150mm至200mm晶圆的产量以及降低MOCVD工艺 的成本,采用能够承受高工作电压和表面电场应力的器件和材料设计。这在100V至600V器件的开发中已经开始实施,预计在未来2至3年这些器

- 12位串行A/D转换器MAX187的应用(10-06)

- AGC中频放大器设计(下)(10-07)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- PIC16C5X单片机睡眠状态的键唤醒方法(11-16)

- 用简化方法对高可用性系统中的电源进行数字化管理(10-02)

- 利用GM6801实现智能快速充电器设计(11-20)