先进3D芯片堆叠的精细节距微凸点互连

时间:05-27

来源:互联网

点击:

上的器件良率。

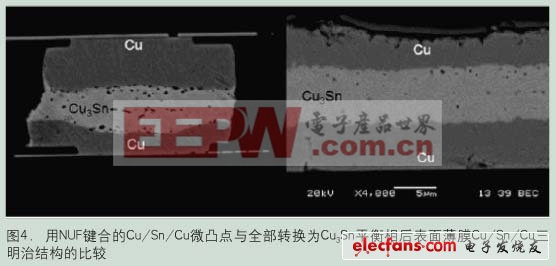

对TLP和SSD键合时空洞的形成也作了研究。除了由于夹带清洗剂残留物形成空洞外,还在Cu3Sn相中观察到名为柯肯达尔(Kirkendall)空洞的较小亚微米空洞,Cu3Sn相在Cu-Sn键合后形成。为了研究制备方法对空洞形成的影响,对不同Cu/Sn/Cu三明治结构做了老化实验。发现空洞最初位于Cu和Sn界面处,但随老化的进展,更多空洞逐步漂离这一表面。在金属间化物连接中心也能观察到大量空洞。Cu/Sn/Cu表面薄膜中也发现柯肯达尔(Kirkendall)空洞,这里三明治薄膜是顺次电淀积形成。不过,将微凸点样品与表面薄膜堆叠(此堆叠持续老化到全都转换成Cu3Sn相为止)比较时,观察到在Cu-金属间化物界面处和在连接中心内的空洞形成密度的不同(图4)。因为Cu/Sn/Cu表面薄膜是用同一电镀化学过程淀积的,不过没有附加还原剂,这些还原剂污染物会增加空洞成核和生长。

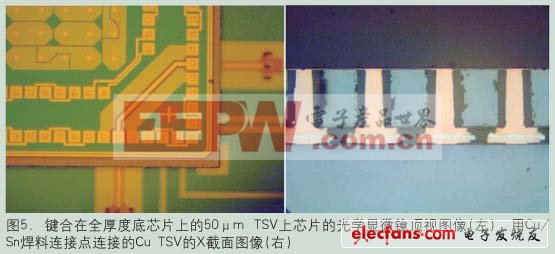

最后,我们说明基于CuSn金属间化物微凸点在用后通孔方法形成的堆叠芯片中的应用。节距为60μm周边阵列TSV的3D晶圆级封装(3D-WLP)TSV器件堆叠在匹配的Si衬底上(图5)。这些器件有菊花链连接,以监控TSV+微凸点连接的电学连续性。观察到Cu-Sn堆叠工艺具有高良率。

结论

用精细节距Cu/Sn微凸点实现薄芯片堆叠。瞬时液相键合和固态扩散键合二者均有高电学良率。

- 多维设计技术力促3D芯片(05-02)

- 新型高线性折叠结构混频器设计(04-27)

- 12位串行A/D转换器MAX187的应用(10-06)

- AGC中频放大器设计(下)(10-07)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- PIC16C5X单片机睡眠状态的键唤醒方法(11-16)