新型高线性折叠结构混频器设计

混频器作为收发机中的关键模块之一,对通信设备的上述性能产生直接的影响。随着微电子工艺的发展, CMOS器件的栅长进一步缩小,MOS器件的过驱动电压也进一步降低,这就为设计低压低功耗的射频电路提供了可能,但是依靠减小MOS器件的栅长降低工作电压是有限的。因此,电路设计者把更多的注意力集中到电路拓扑结构上,使设计具有低压结构的射频电路成为了热门课题。

传统的Gilbert混频器由跨导级、开关级、负载级堆叠组成,其结构自下而上分别为跨导级、开关级、负载级。这种结构中,所有的直流电流都流经跨导级、开关级和负载级,跨导级与开关级电路都需要一个开启电压(VON ) ,负载级也会有一定的电压降(VRL ) , 因此, 电源电压的最小值Vdd,min = 2Von +VRL。如果采用低电源电压,这种结构不能保证所有的管子都工作在饱和区。也就是说, Gilbert混频器不能满足低电压的要求,需要对其做出改进, 如:文献[2 - 3 ]提出省去尾电流管来减小电源电压,文献[ 4 - 11 ]用折叠结构代替堆叠结构来解决上述问题。

文献[ 8 ]给出了折叠结构和堆叠结构的比较,折叠结构增加了两个射频中断电路和一个耦合电容。这样对直流通道来说,跨导级与开关级、负载级的直流电路分开,两条支路相互独立,互不影响。电源电压只需提供相当于一个开启电压(Von )的值就能使跨导管与开关管都工作在各自的饱和区, 即电源电压的最小值Vdd,min = Von + VRL 。达到了低电源电压的目的。但是, 射频中断电路一般用LC 谐振网络实现,电感的使用增加了电路的版图面积和噪声。本文设计了一种新的折叠结构混频器,电路不使用具有大电感的LC谐振电路,工作于1. 2 V 电压时,得到了低电压、低功耗、低噪声和高线性度的性能。

1 电路设计与分析

1. 1 电路拓扑结构

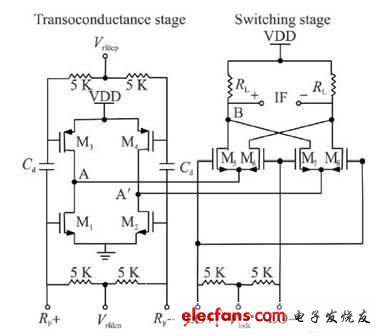

本文设计的折叠混频器拓扑结构如图1所示,M1 ~M4 为跨导级,M5 ~M8 为开关级, RL 为负载电阻。RF输入端接匹配网络, IF输出端接源跟随器作为输出缓冲电路( buffer) 。

图1 交流耦合折叠混频器拓扑结构

该折叠混频器电路的跨导级采用电流复用技术,由NMOS管(M1、M2 ) 、PMOS管(M3、M4 )和隔直电容Cd 组成交流耦合互补跨导结构。跨导级的输出端(A、A′点)与开关管的源极相连。跨导级直接接于电源电压,使得跨导管M1 和M2 的直流电流由两部分组成,一部分来自M3 和M4 ,另一部分来自开关管和负载电阻,达到了低电源电压的目的。

由于流经开关级与负载级的电流很小,这样一方面使得开关管产生的闪烁噪声减小,另一方面负载电阻RL 值可以适当加大,从而提高了混频器的转换增益。所以该电路既满足了低电压的要求,又能保证混频器在低电源电压下有良好的性能。

1. 2 跨导电路设计

图2是几种折叠混频器跨导电路。图2 ( a)在跨导级NMOS管M1 漏端接负载电阻R ,M1 管的电流In 在A 点分流,一部分流经开关管( Is ) ,另一部分流经负载电阻( Ir ) ,但是这种跨导电路的缺点是射频信号一部分通过负载电阻R 泄露到交流地。

为了减少射频信号的损失,必须增加电阻R,这样又会使节点A 的直流电压减小,在低电源电压下,不能保证M1 管工作在饱和区。为了解决这个问题,用有源负载替代负载电阻R ,如图2 ( b) 。但是,这里的PMOS管仅仅增大了节点A与电源电压之间的阻抗,如果把M1 和M2 的栅极连起来,形成CMOS反相器结构,那么M2 在增加阻抗的同时还能跟M1共同放大射频信号 ,如图2 ( c) ,这样就完全避免了射频信号通过M2 泄露到交流地。由图可知, Is =In + Ip ,总跨导gm = gm n + gm p ( gm n是NMOS管的跨导, gm p是PMOS管的跨导) ,所以CMOS反相器有效地提高了混频器的转换增益。

图2 折叠混频器的跨导级几种结构

再来分析一下该结构的直流工作状况,M1 和M2 的栅极加相同偏置电压Vrfdc ,假设Vt 为MOS管的阈值电压, Vovn为M1 的过驱动电压, Vovp为M2 的过驱动电压,则有: Vovn =Vrfdc - Vt , Vovp =Vdd - Vrfdc -Vt ,所以电源电压最小值Vdd,min = Vovn + Vovp + 2Vt。

在0. 18μm CMOS工艺中, Vt 典型值为500 mV,因此用反相器作为跨导电路的混频器只适用于1 V以上的电源电压。为了使混频器能满足更低的电压,在M1 和M2 之间增加隔直电容Cd ,M1 和M2 管偏置分开,如图2 ( d) 。这种结构称为交流耦合互补跨导。假设Vrfdcn为M1 的偏置电压, Vrfdcp为M2 的偏置电压,则电源电压的最小值Vdd,min = Vovn + Vovp + 2Vt+Vrfdcp - Vrfdcn ,可见,在Vrfdcn >Vrfdcp时, Vdd,min比常规反相器更小,适用于更低的工作电压。

1. 3 性能分析

1. 3. 1 增益

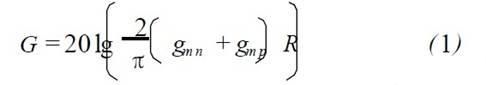

假设本振信号LO为理想方波信号, 则该混频器(如图1)的增益可表示为:

gm n是M1 和M2 的跨导, gm p是M3 和M4 的跨导, R 即负载电阻RL 的值。因为开关管的漏极电流很小,所以负载电阻值可以适当增加,由式( 1)知,混频器的增益将随之提高。值得注意的是,增大负载电阻值的同时必须保证节点A 的直流电压足够使得M1 和M2 工作在饱和区。

1. 3. 2 噪声系数

假设本振信号为理想方波信号,并考虑镜像频率的影响,噪声系数的表达式为:

RS 为源阻抗, RL 为负载电阻值, 系数γn 对长沟道晶体管来说等于2 /3,对于亚微米MOSFET,γn 的值较大。由式(2)知,只要选择合理的偏置电压Vrfdcn、Vrfdcp和M1~M4的宽长比, 噪声系数随着跨导的增加而减小。

1. 3. 3 线性度

如果节点A (见图1)的电压过高,开关管将会关断。也就是说,如果M1 和M3 的电流很大,M1 和M2的输出端电压也增大,这样就会关断开关管M7 和M6或者M5 和M8。开关管进入线性区,影响混频器的线性度,所以降低节点A 的电压,并让开关管远离线性区 ,即Vgs≈Vth ,能提高混频器的线性度。

- 混频器用作开关,可使 DAC 采样频率加倍(01-22)

- 利用运算放大器实现的混频器(06-01)

- 26~40GHz磁调带通滤波混频组件研究(06-26)

- 谐波混频器和谐波检测及控制经典方案汇总,含软硬件设计(11-09)

- 为无线基站选择高线性度混频器(03-25)

- 三混频器技术在混频器测试中的应用(08-04)