DSP实现EAS扫频信号源设计(一)

1 引言

商品防窃监视器(Electronic Article Surveillance)简称EAS,是目前超市普遍使用的安检防窃设备。其原理是由发射电路产生7.8MHz~8.8MHz的扫频信号,该信号由近场天线发射,当天线附近有标签存在时(标签为高Q值的LC振荡回路,谐振中心频率为7.8MHz),标签发出谐振电磁波信号,该信号被EAS接收天线接收,经解调、放大和数字化处理后,最终发出报警信息。传统的扫频信号发生电路由于分立元件参数的一致性差,振荡频率难以精确控制,频率变化的线性度、扫频宽度等诸多指标也受到元件性能的严格约束。笔者采用AD公司的AD9834型DDS实现扫频信号合成,同时,考虑到信号的高速频率变化特点,需使用数字信号处理器(DSP)对AD9834进行控制。笔者采用TI公司的TMS320VC5410型数字信号处理器(以下简称C5410)。下面介绍这些器件的特点及电路实现方法。

2 TMS320VC5410和AD9834简介

本设计要求C5410通过多通道缓冲串行口向AD9834发送命令和数据,由AD9834产生EAS系统需要的扫频信号。C5410是TI公司生产的新一代低功耗TMS320C5000系列定点数字信号处理器,它有3个高速、全双工、多通道缓冲串行口(McBSP),每个串行口可以支持128个通道,速度可达100Mb/s。该系列提供的McBSP支持多种串行通信的方式和协议,可以根据用户的不同需要进行配置。多通道缓冲串行口遵循SPI协议是以主从方式工作的,这种模式通常有1个主设备和1个或多个从设备,其接口包括以下4种信号:串行数据输入(也称为主进从出或MISO);串行数据输出(也称为主出从进或MOSI);串行移位时钟(也称为SCK);从使能信号(也称为SS)。McBSP的时钟停止模式与SPI协议兼容,当McBSP处于时钟停止模式时,发送器和接收器是内部同步的。

AD9834的原理框图如图1所示。它使用的DDS技术是一种利用正弦信号相位线性增加的原理直接由数字累加和数/模转换合成所需频率的技术。AD9834主要由数控振荡器(NCO)、相位调制器、正弦查询表ROM和1个10位D/A转换器组成。数控振荡器和相位调制器主要由2个频率选择寄存器、1个相位累加器、2个相位偏移寄存器和1个相位偏移加法器构成,它的最高工作频率可达50MHz。

AD9834的频率控制字由式(1)求得

式中,0Δphase228-1,fMCLK最高可达50MHz,它是由高稳定度晶体振荡器获得或由其他器件编程提供,用来同步整个合成器的各个组成部分。

相位控制字由式(2)求得

ΔP=Kx2π/4096 (2)

式中,0小于K小于228-1,改变K值即可改变输出相位值。

3 系统设计思想

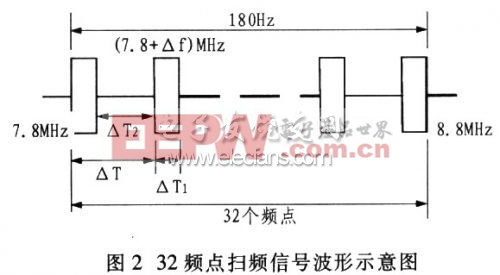

传统的EAS扫频信号产生电路使用了压控振荡集成电路。通过改变外围变容二极管的直流偏压可以使扫频信号的频率范围控制在8.2MHz±0.5MHz。当采用全数字频率合成时,由于数字信号的非连续性,不可能产生连续的扫频信号,只能产生台阶性变化的扫频信号,即1个单频点持续一段时间后增加4,,再跳跃到另1个单频点,因此,如果扫频信号的扫频 范围为8.2MHz±-O.5MHz,将该lMHz频率跨度等分为32个频点,于是相邻频点之间的频率间隔Δf=1MHz/31=0.0323MHz。如果扫频信号的扫频周期为 180Hz(即5.6ms),则每个频点占用的时间为ΔT=5.6ms/3l=181pμs。该ΔT又分为二部分,第一部分△T1为振荡时间,即单频率波形持续时间;第二部分ΔT2为延时等待时间,在这段时间内理论上没有波形输出。在实际应用中可通过动态改变△T2在ΔT中所占的比例以控制EAS的发射功率,对系统很有用。如果每个单频率波形持续时间(频率振荡时间)△T1=10μs,则每个单频率波形的延时等待时间ΔT2=(5.6-0.01x32)/31=170.3μs。多通道缓冲串行口发送1个单频率字只需71μs左右,能够完成控制字和频率字的发送,而且还能够在此时间内完成复杂的计算。图2为180Hz周期内完成的32频点扫频信号波形示意图。其中,每个频点展开后都是频率一定的正弦波,每个周期内32频点扫频信号的频率范围都是从7.7MHz到8.7MHz台阶性变化。

4 硬件设计方案和软件实现

4.1 硬件设计方案

基于上述设计思想的硬件连接方案如图3所示,包括C5410、10MHz晶体振荡器、AD9834及滤波放大电路。由于AD9834的电源电压在2.3V到5.5V范围内可选,C5410的电源电压为3.3V。所以在连接时无需电平转换。10MHz晶体振荡器向C5410提供输入时钟。初始化C5410使其工作频率为100MHz,因为只有此时才能使其定时器周期寄存器从TOUT引脚输出50MHz时钟信号。该时钟信号输出到AD9834的MCLK脚,作为AD9834的工作时钟。理论分析指出:输出信号的相位噪声取决于时钟信号的相位噪声,在输出信号频率不变的情况下,输入时钟信号频率越高,相位噪声恶化越小。

滤波放

- 单片式降压型稳压器为DSP提供片内电源排序(01-09)

- 什么是PCI总线?其接口芯片的应用(01-26)

- 功率分配系统(PDS)设计:利用旁路电容/去耦电容(04-29)

- 具有多个电压轨的FPGA和DSP电源设计实例(05-22)

- 具有多个电压轨的FPGA和DSP电源设计实例(二) (05-22)

- 基于DSP和CPLD的移相全桥软开关电源数字控制器(06-02)