噪声频谱密度——一项“新”的ADC指标

时间:02-11

来源:电子产品世界

点击:

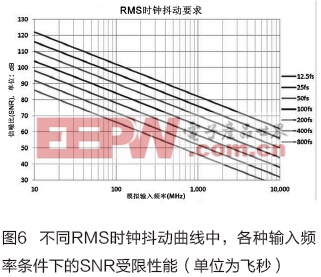

下,仅由孔径抖动(tJ)造成的信噪比(SNR)下降计算公式如下:

SNR = 20 × log10[1/(2 × π × fA × tJ)]

如图6所示, 随着输入频率增加,需要较低的RMS时钟抖动,才能实现较低输入频率下同样的SNR限制。 例如,200飞秒(fs)的RMS时钟抖动会将ADC的SNR性能限制为低于70 dB(250 MHz下)。 但是,1 GHz的输入信号需要50飞秒或更好的RMS时钟抖动,才能实现同样的70 dB SNR性能。

ADC的噪声频谱密度可简单定义为ADC的满量程信号功率减去噪声功率,然后分布在1 Hz带宽单位增量上。 FFT采样深度变化并不影响ADC的噪声频谱密度。 它只会将噪声分布在不同的单位频率带宽上。

噪声形状可能会有所不同,具体取决于ADC架构以及是否使用数字滤波器来滤除带外噪声。 对于带宽远大于系统要求的奈奎斯特速率ADC,处理增益可提高目标带宽内的动态范围。

SNR ADC NSD 噪声 FFT 201503 相关文章:

- 抖动和SNR详解(11-23)

- 时钟抖动时域分析(二)(02-20)

- 低功耗 ADC(04-06)

- 14位、125 MSPS四通道ADC,通过后端数字求和增强SNR性能(11-27)

- 了解ADC信号链中放大器噪声对总噪声的贡献(03-30)

- 如何处理高电压输入却不损失SNR(05-15)