噪声频谱密度——一项“新”的ADC指标

计引入的非线性会将其实际SNR限制为小于理想值。 换种方式来看,如果我们从ADC满量程输入功率中减去信号功率,则余下的正好是总噪声功率。 如果我们将NSD数量中的所有1-Hz噪声子元相加,则可以得到单独的功率噪声量,等于ADC满量程功率减去信号功率。

要确定奈奎斯特速率ADC的NSD值,必须计算噪声在奈奎斯特区的分布,然后从满量程信号功率中减去。 要开始计算,必须知道采样速率。 让我们以理想的12位200 MSPS ADC为例,它具有理想的满量程SNR,即6.02*12 + 1.76 = 74.04 dB。 其噪声分布在100 MHz奈奎斯特区域(Fs/2)内。 每个1 Hz子元的噪声可使用每个子元噪声功率的对数函数来计算,即–10Log10(Fs/2) = –80 dBFS/Hz。 对于这个12位理想转换器,NSD将为:

–74.04 – 80 = –154.04 dBFS/Hz

因为实际生活中并没有理想ADC,所以我们必须找到ADC的实际SNRFS。 这可通过直接测量得到,也可以从制造商的数据手册中找到。

ADC的满量程输入信号功率水平可以使用已知的满量程峰值电压或满量程RMS电压以及ADC的输入阻抗来计算。 如果输入电压和输入阻抗都是已知的,则可以计算满量程功率(单位dBm),其中:

Vrms = Vp/√2 or Vp x 0.707

信号功率 = ((Vrms2)/Rin)(单位为W)

对于满量程信号功率(单位为dBm):

信号功率 = 10 x log(((Vrms2)/RIn) x 1000 mW/W) = 10 x log((Vrms2)/Rin) + 30 dB

ADC量化噪声频谱是什么形状的? 它总是平坦的吗?

奈奎斯特速率ADC以要求的最低采样频率工作,以便捕捉关于整个输入带宽的所有信息。 多数采用流水线型、逐次逼近寄存器(SAR)型或Flash型架构的奈奎斯特速率ADC都有量化噪声,在DC到奈奎斯特频率范围内该噪声基本平坦。 这样,这些器件将成为“机会均等”的噪声接收器,相等地接收整个Fs/2频谱中的有限功率量化噪声(图2)。

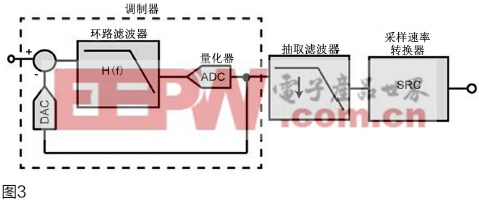

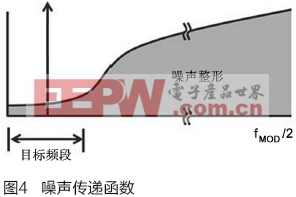

对于不需要完整奈奎斯特带宽的应用,可以实施替代ADC架构。 带通连续时间Σ-?(CTΣΔ或CTSD)型ADC使用噪声整形功能,其本质就将带内量化噪声“推出”或者从目标频带中滤除。 这将导致噪声传递函数在目标窄带(小于奈奎斯特带宽)内具有低陷的非平坦形状。 在此带中,CTSD ADC的工作性能最高,并且SNRFS达到最大(图4)。

由于CTSD架构的主要优点之一是能够检测狭窄频带内的信号,因此宽带NSD并不是很重要。 相反,狭窄通带内的动态范围将突出为CTSD ADC的性能指标。 噪声整形传递函数将基于调制器设计中使用的环路滤波器阶数来确定。

ADC的处理增益对噪声密度和SNR有何影响?

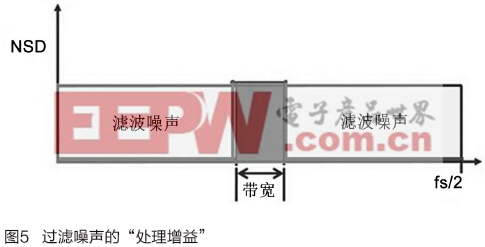

在一些应用中,主要目标信号仅位于很小的带宽(BW)内,比奈奎斯特带宽小很多。 这时,可使用数字滤波器来滤除较小带宽之外的噪声。 此过程实现方式为,在从奈奎斯特速率ADC输出数据前,使用数字下变频级来抽取、调谐和过滤数据。 这时,我们的SNR计算必须包含此滤波过程的校正系数,该系数就是过滤噪声的“处理增益”(图5)。

理想SNR(含处理增益)= 6.02*N + 1.76 dB + 10log10(Fs/(2*BW))

假设我们使用的是采样频率为100 MSPS的奈奎斯特速率ADC,但是,我们的系统应用不需要观察转换器的整个50 MHz奈奎斯特带宽。 相反,我们仅希望观察奈奎斯特带宽中较小的八分之一部分,即20 MHz和26.25 MHz之间的6.25 MHz带宽部分。 如果我们实施数字滤波算法并将滤波器调谐到此目标带宽,可以计算得到因过采样而产生的+9 dB处理增益:

处理增益 = 10log10(Fs/(2*BW)) = 10log10(100*106/(2*6.25*106)) = 10log10(8) = 9 dB

带宽每减少2次幂,因过滤噪声而产生的处理增益就会增加+3 dB。 这可从上例中看出,带宽减少(1⁄2)3会产生3 x 3 dB的处理增益。

还有哪些配套元件可影响系统中ADC的NSD性能?

许多外部因素都可导致高速ADC的最佳性能下降。 这会造成SNR下降而有效噪声密度升高。 任何影响ADC的SNRFS或采样速率的补充元件都有可能影响系统中ADC的NSD。 让我们来重点看看时钟抖动,这是造成ADC在高采样频率时SNR性能下降的常见元凶之一。

高速、高分辨率ADC对时钟输入信号的质量非常敏感。 要在高速ADC中实现出色的SNR性能,必须根据应用的输入频率要求,仔细考虑均方根(RMS)时钟抖动。 即便是在性能最高的ADC中,RMS时钟抖动也可能限制SNR,在较高输入频率时问题更为严重。 虽然这不会改变ADC的NSD潜在能力,但在具有高抖动时钟的系统中会限制其实际SNR性能。

使用相同的RMS时钟抖动时,ADC的模拟输入频率每翻三倍,最佳的SNR性能便会下降10 dB。 在给定的输入频率(fA)

SNR ADC NSD 噪声 FFT 201503 相关文章:

- 抖动和SNR详解(11-23)

- 时钟抖动时域分析(二)(02-20)

- 低功耗 ADC(04-06)

- 14位、125 MSPS四通道ADC,通过后端数字求和增强SNR性能(11-27)

- 了解ADC信号链中放大器噪声对总噪声的贡献(03-30)

- 如何处理高电压输入却不损失SNR(05-15)