基于软件解调的新型NAVTEX信号处理单元研制

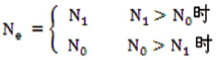

码元内Nf个数据比特中0和1的个数,设0的个数为N0,1的个数为N1,则

其中假设Ne为当前码元中错误比特的个数,

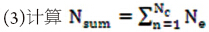

(2)如步骤1的算法,分别计算Nc-1其余码元中的Ne。

(4)比特同步窗左移或右移1比特,按照步骤1-3的方法计算Nsum2,并比较Nsum和Nsum2。

当Nsum2>Nsum时,向相反方向移动,并循环1-3的步骤;

当Nsum2sum时,继续原移动方向,并循环1-3的步骤。

(5)移动Nf个数据比特,可计算出 min(Nsum),即实现了比特同步。

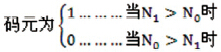

(6)计算比特同步后每个码元的为N0 和N1,实现码元判决。

3 新型NAVTEX信号处理单元设计

基于上述的软件解调原理,改进了传统NAVTEX接收机的信号处理模块,采用基于DSP处理器的信号处理电路,通过上述软件算法,研制了新型的NAVTEX接收机。

3.1 硬件设计

硬件设计主要包括A/D转换和DSP数字处理器电路,采用高保真音频采集芯片TLV320AIC23B进行A/D采集,将1700Hz的模拟音频信号进行A/D转换,并通过数字信号处理芯片(TMS320VC5402)进行数据处理,完成软件解调,并将解调的NAVTEX报文输出至显示单元进行信息显示。

3.2 软件设计

NAVTEX模拟音频信号两个载频分别为1615Hz和1785Hz,数据码元长度为10ms,即

f1=1615Hz; f2=1785Hz; N=10ms;

根据奈奎斯特采样定律,结合采样芯片TLV320AIC23B,选取采样频率fs=8000Hz;则每个码元长度内采样点的个数Ns=10ms×8000Hz=80个。

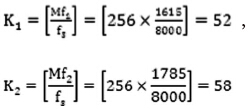

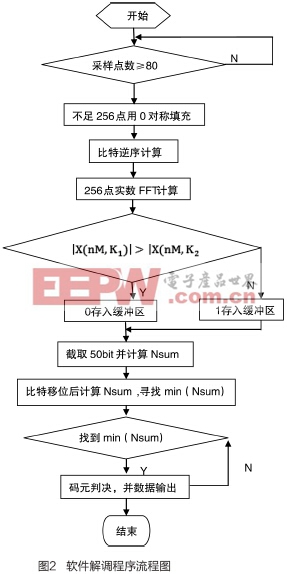

取信号截取长度80,即截取80个采样点进行短时傅立叶变换,为了提高频率分辨率,设计采用256点FFT,除80个采样点外,其余点补0,则计算

即每次傅立叶变换后计算第58个谱线的幅值|X(nM,58)|和第52根谱线的幅值|X(nM,52)|并比较其大小。取移动窗移动步长为Ls=8,则每个码元内的短时傅立叶变换的次数

取Nc=5,即使用5个码元长度作为作为比特同步窗,即50个比特作为比特同步和码元判决窗。软件解调流程图见图2。

4 结论

本设计采用基于短时快速傅立叶变换的软件解调算法,对传统NAVTEX接收机的硬件解调电路进行了改进,解决了传统解调所固有的随环境变化而灵敏度下降的缺点,现改进后的NAVTEX接收机已进入批量生产阶段,工作效果达到预期效果。

参考文献:

[1] 庞福文.汉字奈伏泰斯系统论[M].大连:大连海事大学出版社,2001

[2] 樊昌信,等.通信原理[M].北京:国防工业出版社,2001

[3] 杨小牛.软件无线电原理与应用[M].北京:电子工业出版社,2001

[4] 王兴亮.数字通信原理与技术[M].西安:电子科技大学出版社,2009

[5] 冷建华.数字信号处理[M].国防工业出版社,2014

[6] 曲丽荣.短时傅立叶变换在数字信号处理中的应用 [J].科技资讯.2007,(27)

[7] 李伟光,李静,葛临东. 一种基于DSTFT解调FSK信号的改进方法[J].现代电子技术,2006,(6)

[8] 陈忠辉,林海斌,陈新.基于DSTFT的FSK信号的解调[J].现代电子技术,2008,31(23)

NAVTEX DSP 射频 2FSK 傅立叶变换 201501 相关文章:

- 单片式降压型稳压器为DSP提供片内电源排序(01-09)

- 什么是PCI总线?其接口芯片的应用(01-26)

- 功率分配系统(PDS)设计:利用旁路电容/去耦电容(04-29)

- 具有多个电压轨的FPGA和DSP电源设计实例(05-22)

- 具有多个电压轨的FPGA和DSP电源设计实例(二) (05-22)

- 基于DSP和CPLD的移相全桥软开关电源数字控制器(06-02)