HDMI前端设计与实现

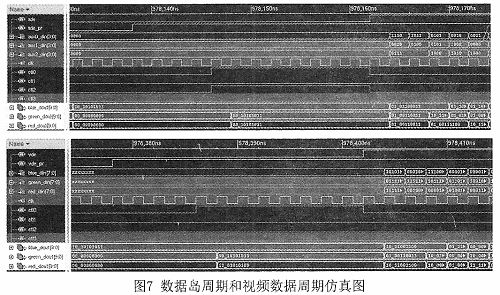

nd的时钟周期之后,进入下一个状态,ctl[3:0]的值与状态所表示的值对比便可验证。

在验证数据岛周期:在ade_pr置高位后,经过4个blanking+8个preamble+2个leading guard band。packet传输结束后置低位。ade置高位进入data island period,再经过2个leading guard band+N个32位的packets+trialing guard band。trialing guard band后置低位。在8个preamble时,ctl[3:0]=4’b0101。

在验证视频数据周期时:vde_pr置高位后,经过4个blanking+8个preamble+2个leading guard band。video data传输结束后置低位。vde置高位进入video data period,再经过2个leading guard band+active video pixels。video data传输完后置低位。在8个preamble时,ctl[3:0]=4’b0001。

图7数据岛周期和视频数据周期仿真图

3.2 HDMI模块仿真

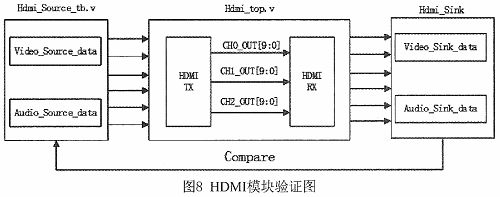

把时钟模块和encoder模块整合成TX模块,其中encoder模块分别实例为Encdr、Encdg、Encdb三个信道的编码模块。将TX和RX模块,即hdmi_encoder和hdmi_decoder,组合在一起仿真。

如图8所示,输入的音频、视频数据用random函数随机产生,且在固定的时间周期输入,将输出与输入对比,得出HDMI整个编解码模块是否正确。

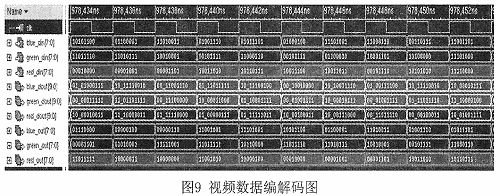

如图9所示,第一组为7bits视频数据输入,第二组为编码后的10bits视频数据输出,第三组为解码后的7bits视频数据输出。视频数据编码需要三个时钟,解码需要两个时钟,所以每间隔五个时钟输入7bits数据等于输出的7bits数据,即从编码到解码一共需要五个时钟。

4 结论

进入21世纪,在带宽、音频、传输安全等方面具有优越性的HDMI的出现,满足了数字高清时代海量数据流传输的需求。本设计运用 verilog HDL实现HDMI编码及解码功能,通过写仿真测试激励及运用NC—Verilog工具仿真代码逻辑的正确性。从子模块、模块、系统仿真验证自底向上的方法来进行,最终根据仿真验证结果确认实现编解码功能。非常感谢芯珠微电子林泉工程师及梁文锋、黎伟莲、洪传练、杨家昌等同事的帮助,本设计的不足之处将在后续工作中改进。

- 模拟信号的原理(02-14)

- 光电编码器在电机控制中的应用(03-02)

- 音频编码标准发展现状及发展趋势(04-19)

- 视频编码讲坛之H.264前世今生(05-18)

- 支持热调节和输入过压保护功能的安全增强型线性锂电池充电器(08-16)

- 新一代视频编码标准H.264/AVC的关键技术研究(09-04)