HDMI前端设计与实现

One Bit音频。

2 HDMI编码设计

本设计是基于HDMI 1.4版本的编解码设计。主要分为两个大模块设计,即HDMI TX编码模块和HDMI RX解码模块。TX编码模块主要实现把视频、音频数据通过编码传输给Rx解码模块。RX解码模块主要把视频、音频数据解码后传输给外置设备。

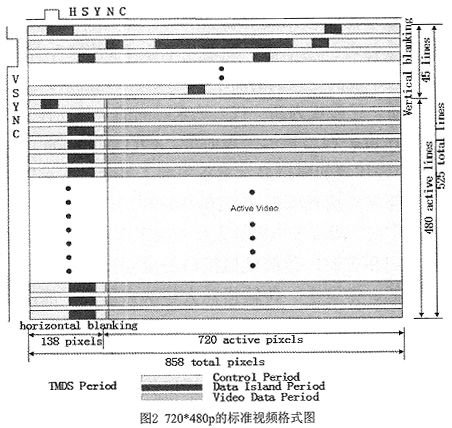

如图2所示,HDMI有三种处理数据的操作模式:视频数据周期,数据岛周期,控制周期。在视频数据周期,传输每一个有效的视频像素行。在数据岛周期中,音频和辅助数据使用一系列数据包来传输。在音频和视频周期的两个非控制周期之间要插入控制周期。

视频数据周期采用最小化差分传输编码(TMDS)的编码方式,对每个8bits传输信道进行编码,三个传输信道共24bits数据。

数据岛周期采用TMDS纠错编码(TERC4)的编码方式,每个4bits传输信道进行编码,三个传输信道共12bits数据。

控制周期采用最大化传输编码的编码方式,对每个2bits传输信道进行编码,三个传输信道共6bits。这6bits数据包括HSYNC、VSYNC、CTL0、CTL1、CTL2、CTL3。在每个控制周期的末尾有一个报文头,使用CTLx bits数据组成的preamble,指示下一个数据周期是视频周期还是数据岛周期。

每一个数据岛周期起始于前导保护带(Leading Guard Band),结束于后置保护带(Training Guard Band);而视频数据周期只始于前导保护带,没有后置保护带。保护边界两个特殊字符组成,设计目标是提供从控制周期到数据周期或从数据周期向控制周期转化的鲁棒决策。

下表2.3展示在数据传输中每种操作模式的编码类型。

2. 1 编码器TX模块

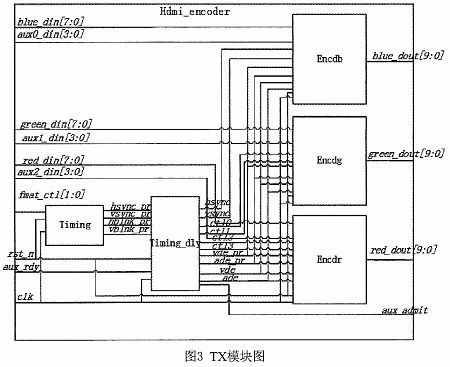

TX(信源端)发射模块,包括时钟模块(由Timing和Timing_dly两个模块组成)、以及编码模块。时钟模块主要为视频音频交错相传产生时钟,编码模块实现对视频音频数据编码传输。

2. 1.1 时钟模块

(1)Timing模块

Timing模块是HDMI编码器的基础,它产生720*480p、1280*720p、1920*1080i等视频格式的行信号hsync_pr、场信号vsync_pr、行无效信号hblnk_pr和场无效信号vblnk_pr。如图2所示,hsync_pr、vsync_pr分别为HSYNC、 VSYNC;hblnk_pr为每行前138 pixels置高位,vblnk_pr为每帧前42行和后3行共45行置高位(注:具体定义以CEA-861-D中规定的720*480p的标准视频格式为准)。

(2)Timing_dly模块

Timing_dly模块是HDMI高速数据传输的核心,按照TMDS通道的视频音频交错传输数据要求,分配视频数据、音频数据和辅助数据,以及控制数据的传输时间周期,并为编码模块提供控制信号。

主要端口定义:

hsync_pr、vsync_pr;行信号和场信号。

aux_rdy:当输出是“1”,则外部数据缓存音频数据准备完毕,可以传输音频数据;否则,音频数据未完成打包,终止传输音频数据。

aux_admit:当输出是“1”,则传输音频数据;否则终止接受音频包数据。

ade、vde:分别表示传输音、视频数据标志位,为高时表示进入数据岛或视频数据周期。

2.1.2 encoder模块

timing模块采用TMDS编码、TERC4编码和最大化传输编码三种编码形式,对视频数据、音频数据包和辅助数据、控制数据编码传输。

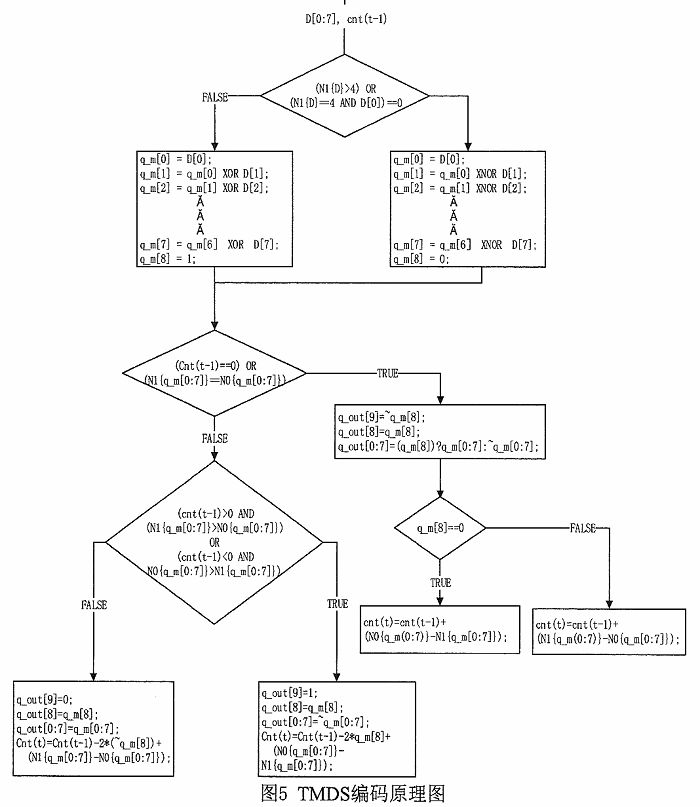

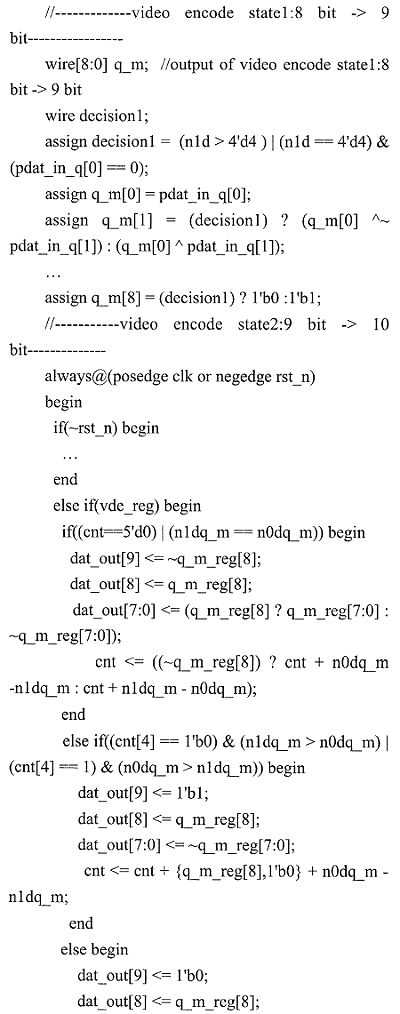

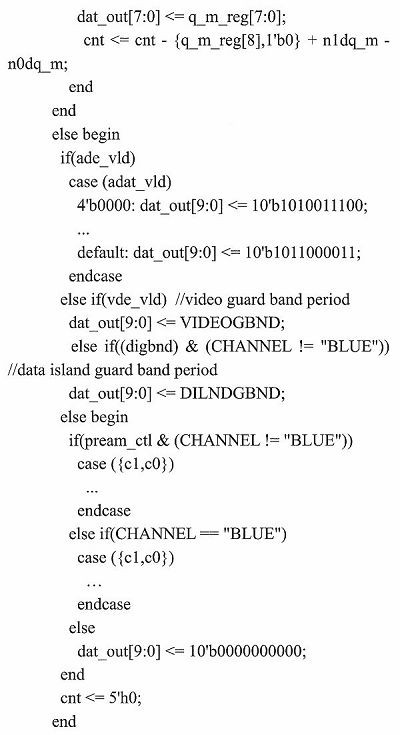

视频像素数据的编码可分为两个阶段:第一个阶段是输入音频的8bits像素数据转换成9bits数据;第二阶段是把9bit数据转换成TMDS传输10bits。

实现的TMDS编码算法如图5所示。

D:输入8 bits视频数据。

cnt:计算编码数据中0和1个数的差值。若cnt为正值表示发送1的数量超过0的数量,负值则表示发送0的数量多于1的数量。cnt{t-1}表示相对于输入数据的前一个周期的cnt的值,cnt{t}表示本周期的值。

q_m:第一阶段的9 bits输出数据。

q_out:第二阶段的10 bits输出数据,即编码器输出值。

N1{x}:这个操作符返回参数x中的1的个数。

N0{x}:这个操作符返回参数x中的0的个数部分核心代码如下:

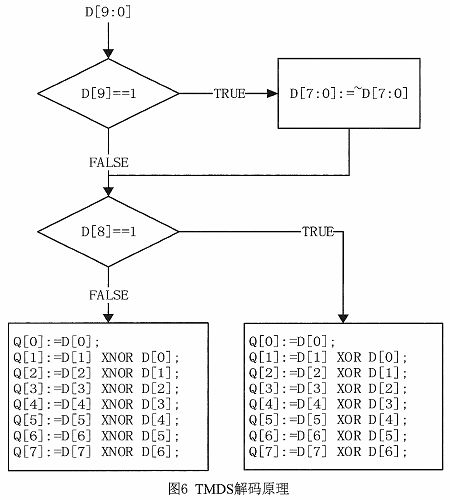

2.2 解码器RX模块

解码器模块较容易实现,只需依据preamble控制位判断接下来传输的数据类型,即音频或视频数据,然后解码即可。解码同样分两个阶段,如图5所示,第一阶段由10bits数据转为9bits数据,第二阶段由9bits数据转为8bits数据。

图6 TMDS解码原理

3 HDMI功能仿真验证

在HDMI功能验证采用分层验证法,根据Spec1.4的编码解码的要求,制定验证计划,设计各种激励,实现近百分之百的覆盖率。本文运用的工具是Cadence NC—Verilog,文中介绍部分验证计划,以及验证的结果。

3.1 时钟模块的功能仿真验证

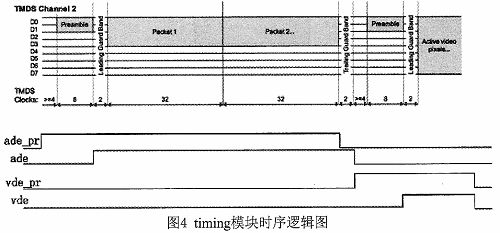

按Spec1.4要求,给定仿真必需激励信号,仿真数据岛周期及视频数据周期的每个像素时钟的功能分布是否符合Spec1.4的要求。比如验证ctl[3:0]的正确性,如图4所示,在3个blanking、8个preamble、2个leading guard ba

- 模拟信号的原理(02-14)

- 光电编码器在电机控制中的应用(03-02)

- 音频编码标准发展现状及发展趋势(04-19)

- 视频编码讲坛之H.264前世今生(05-18)

- 支持热调节和输入过压保护功能的安全增强型线性锂电池充电器(08-16)

- 新一代视频编码标准H.264/AVC的关键技术研究(09-04)