基于DSP的某导航计算机模块的设计

摘要:随着现代导航技术的发展,惯性导航作为一种自主导航技术已经广泛应用于多种武器系统中,而导航计算机又是捷联式惯导的核心部件。文章提出了一种采用基于DSP的某型导航计算机模块的解决方案,设计方案采用双处理器TMS320C6713,对数字电路接口实现了光电隔离,采用 FPGA实现对多路信号的核心处理,并具有CAN总线通信接口。本文对计算机单元的硬件设计与实现方法进行了较为详尽的描述。该计算机单元满足了某型武器惯性导航系统的使用需求。

引言

随着现代武器技术的发展,作为惯性导航系统控制核心的计算机单元,其一体化和集成度越来越高、接口越来越丰富。本文以某型导航计算机模块的需求作为背景,介绍了一种基于双DSP(TMS320C6713)和FPGA的计算机模块的硬件设计与实现方案,较好得满足了导航计算机的各控制需求,同时具有小型化和一体化的特点。

1 总体设计

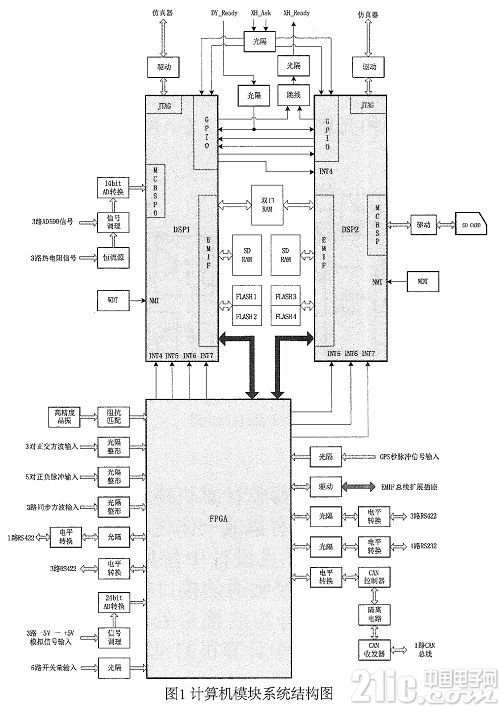

导航计算机板由两个DSP构成,主要功能是定时采集三路陀螺正交编码信号、三路加速度计的输入和里程计输入信号,并对采集的数据进行必要的处理,以实现导航解算;同时将采集数据通过RS422总线和CAN总线发送给地面监测设备;通过RS422总线接收相关的命令和相关的参数。计算机系统结构见图1所示。

计算机单元各控制接口丰富,其主要功能模块包括:处理器相关电路、正负脉冲信号处理电路、正交方波信号处理电路、异步串行接口电路、AD测温电路、CAN总线接口电路、开关量输入输出电路、模拟量输入电路、电源转换电路和FPGA等。

2 详细设计

由于计算机单元接口众多,在详细设计中仅对主要的以下电路作出介绍:处理器相关电路、正负脉冲信号处理电路、正交方波信号处理电路、AD测温电路和CAN总线接口电路。

2. 1 处理器及其外围电路

处理器及其外围电路包括双TMS320C6713处理器、时钟电路、JTAG驱动电路、复位电路、存储器电路。

双DSP各自具有不同的控制功能分工,两者均通过各自的EMIF局部总线和FPGA通信,访问和控制FPGA中不同的控制功能模块,两者之间可以通过双端口RAM存储器实现互相通信。

处理器最高工作频率200MHz,最大处理能力1200MFLOPS,通过EMIF局部总线实现对SDRAM和FLASH存储器的无缝接口,单片支持4路外部中断,片内两路32位定时器。

2.2 正负脉冲信号处理电路

信号形式为正交方波信号(需隔离、整形),5V TTL信号,正交方波信号先经过RC滤波电路和保护二极管,然后经过光隔进入FPGA。

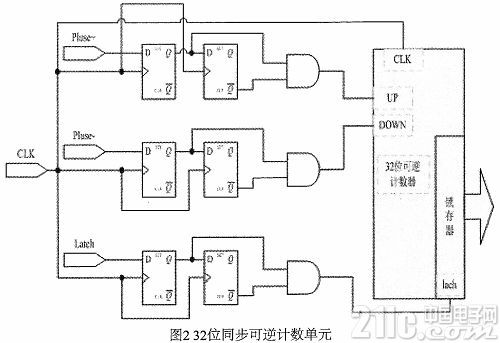

5路正负脉冲信号输入为可逆脉冲,频率最高256KHz,每个通道加速度计输入包括3路信号,分另0是G+(H+、I+、E+、F+)、G-(H-、 I-、E-、F-)、GND(公共地),G+信号上有脉冲时计数值增加,G-信号上有脉冲时计数值减少,上电默认值为满量程的中间值,当采样时钟中断产生时,将计数结果存入锁存器内。设计时5路信号分别采用32位同步可逆计数单元来实现,正负脉冲和锁存信号均经同步处理,同步时钟为DSP1的系统时钟,锁存信号为经分频后的采样时钟S_CK。32位同步可逆计数单元结构图如图2所示。读一次锁存器内的32位计数值需进行两次读操作,分别读出低16位和高 16位数值,然后整合。

2.3 正交方波信号处理电路

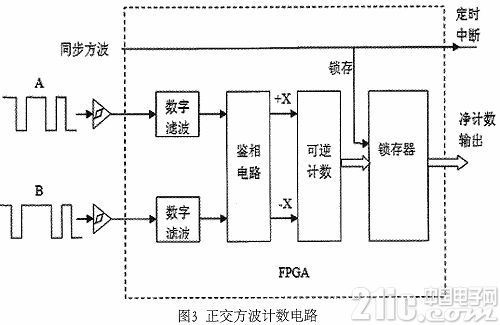

3对正交方波信号由3个通道输入,每个通道包括A+A-、B+B-、C+C-信号和各自独立地线。信号形式为正交方波信号(需隔离、整形),5V TTL。

当A+相超前A-相90度时计数值增加,当A+相落后A-相90度时计数值减少,频率最高1MHz。信号进入FPGA后首先进行数字滤波处理,滤波后的信号再进行鉴相,产生四倍频的可逆脉冲信号,然后对可逆脉冲进行计数,当同步方波中断产生时,将计数结果存入锁存器内。信号在滤波后鉴相,得到可逆脉冲后进入32位同步可逆计数单元(图2),此时的同步时钟为DSP1系统时钟,锁存信号为同步方波中断。正交方波计数电路原理如图3。

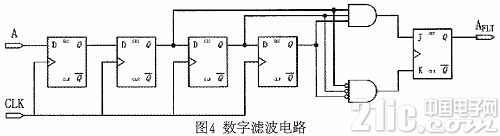

信号进入FPGA后经过一个4位延迟数字滤波器,数字滤波器参考了积分解码器/计数器芯片HCTL2000的设计,原理如图4所示。根据原理图,数字滤波器的输入信号必须在三个连续的时钟上升沿保持同一电平,才能够通过4位延迟移位寄存器,因此小于两个时钟周期的噪声脉冲都被抑制掉。

每路正交方波的两个信号经过数字滤波器输出后,进入鉴相电路,经过处理后,变为四倍频的可逆脉冲信号,鉴相电路原理见图5所示。以X正交输入为例,两路输入信号A、B分别经过两级移位寄存器,A经过第二级的输出信号命名为C,B输出信号分别是D,最后输出分别得到正、负通道信号+x和-X,(A D)(not(B

D)(not(B C)),-X=(B

C)),-X=(B C)(not(A

C)(not(A D))。这种鉴相电路具有较强的抗干扰能力,即使A或B输入上有噪声信号通过前面的滤波电路,也会在+X和-X上产生对称的脉冲而互相抵消掉,最后信号输入至32位同步可逆计数单元(图2)。

D))。这种鉴相电路具有较强的抗干扰能力,即使A或B输入上有噪声信号通过前面的滤波电路,也会在+X和-X上产生对称的脉冲而互相抵消掉,最后信号输入至32位同步可逆计数单元(图2)。

- 单片式降压型稳压器为DSP提供片内电源排序(01-09)

- 什么是PCI总线?其接口芯片的应用(01-26)

- 功率分配系统(PDS)设计:利用旁路电容/去耦电容(04-29)

- 具有多个电压轨的FPGA和DSP电源设计实例(05-22)

- 具有多个电压轨的FPGA和DSP电源设计实例(二) (05-22)

- 基于DSP和CPLD的移相全桥软开关电源数字控制器(06-02)