半导体器件的电气过应力和静电放电故障

正常器件略高,但仍可能在数据表限制范围以内。在氧化物硬击穿中,器件无法工作,从栅极到通道形成电流路径,晶体管被破坏。

栅氧化层损坏是ESD事件中最常见的。栅氧化层击穿取决于氧化物的厚度、偏置电压、氧化物材料的击穿电压、氧化物膜的均匀度和粗糙度等。如氧化物膜有尖锐边缘,那么感应电场会高度集中在边缘上,很可能被击穿。

假设氧化物层厚度为100A0而氧化物层上的电压为3.3V,那么氧化物层上的平均电场计算如下:E=V/Tox

氧化物或电介质击穿

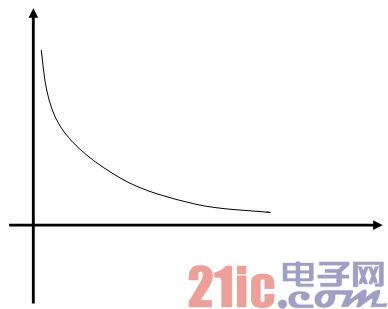

电介质材料二氧化硅的击穿电场为11x106V/cm。如氧化物厚度减为50A0,E=6.6x106V/cm且电介质间的电场增加,就会趋近于击穿。如V为常量不变,E.Tox=常量,这是一个双曲线方程式(XY=C)。图8给出了电场和氧化物厚度的曲线。

图8:电场和氧化物厚度

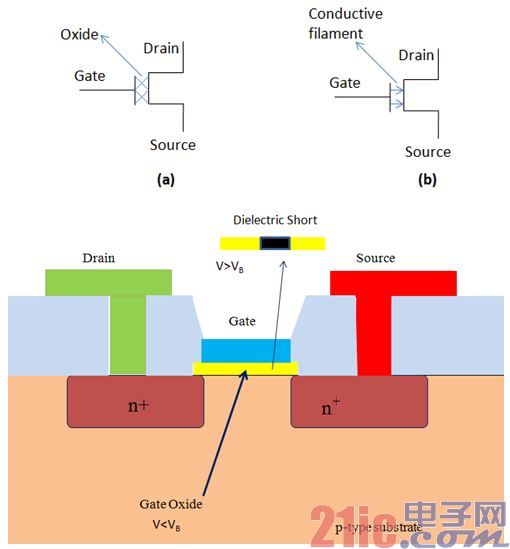

图9:(a)ESD脉冲前的栅氧化层、(b)受到破坏的氧化物形成的细丝和(c)V>VB电介质短路等原理图

氧化物击穿有以下机制:氧化物层上的电压超过氧化物(电介质)的击穿电压(V>VB),这样栅氧化层会被击穿,氧化物层上形成较低电阻或传导路径。由于电流流过路径的电阻减小(氧化物或电介质击穿),会出现电介质的局部升温。由于局部温度较高,传导位置熔化,形成细丝,进而导致电介质上的金属层短路,如图9所示。氧化物击穿是CDM的主要击穿机制。

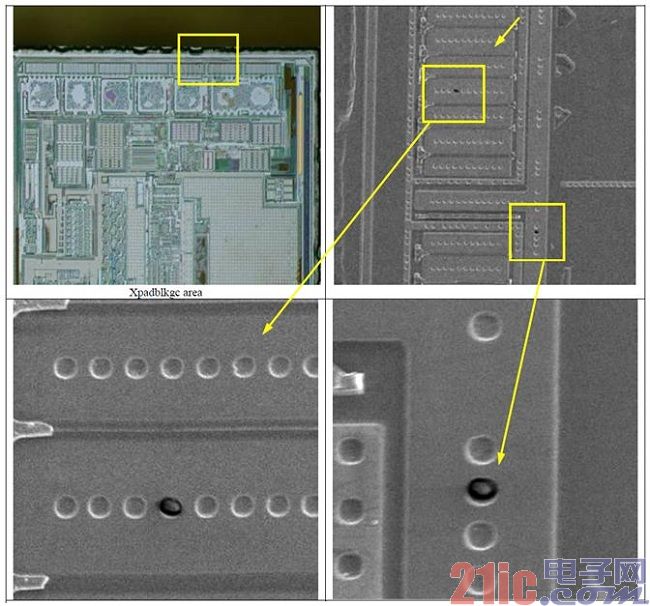

图10:栅氧化层破裂

图10给出了ESD-CDM事件中出现氧化物破裂的情况。在故障部件中,测试台没有观察到输出。在电隔离情况下,振荡器电路的参考输入引脚处观察到高漏电。振荡器模块的参考输入引脚电容处也检测到热点。

图11显示了没有观察到输出的晶体振荡器的ESD损坏情况。测试台(I-V曲线跟踪)显示OE(输出启用)引脚处有4.3mA的漏电。故障点隔离用Hamamatsu emission/OBIRCH显微镜检查实现,将问题局部化。在故障引脚的输入电路上检测到热点。随后采用等离子/化学蚀刻进行物理分析发现emission microcopy识别的热点区域存在引脚孔。

图11:I-V曲线跟踪、热点和引脚孔的图示

接触毛刺或结点损坏

接触毛刺或结点损坏是指p-n结点因ESD事件造成的焦耳热效应损坏。当芯片加热后,共价键被破坏并生成电荷载体,而芯片的电阻率和热传导性随着温度升高而降低。

图12:接触损坏的SEM图

ESD脉冲作为一个电流源。当ESD脉冲突然施加到芯片上时,会加热不均匀。局部区域在绝热条件下加热,较高电流提升结点温度,并超过芯片的熔点,从而造成结点熔化。图12显示ESD造成的接触损坏。ESD产生的能耗引起接触毛刺或结点损坏,其计算如下:

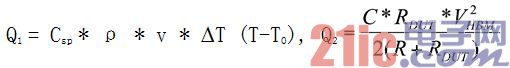

在绝热条件下,ESD事件产生的能量等于结点吸收的能量:Q1=Q2

其中,

假设Q1=Q2

Csp=具体热容量,ρ=密度,T0=初始温度

如果T≥Tm(熔点),那么就会出现结点熔化。

Wunsch Bell模型采用以下热扩散方程式,这是描述结点击穿的最常用模型。在此模型中,结点击穿现象由脉冲宽度和器件施加的功率密度决定。

其中,P=以瓦特为单位的故障功耗,A=以平方厘米为单位的面积,Cp=以J/gcm-K为单位的热容量,ρ=以g/cm3为单位的密度,κ=以W/cm-K为单位的热传导,t=矩形脉冲宽度,Tm=结点熔化温度,而T0=初始温度。

以上方程式说明了温度、ESD脉冲电压、故障功率和材料熔点之间的关系。

- 太阳能发电系统对半导体器件的需求分析(06-09)

- 柔性非晶硅薄膜太阳电池技术(05-11)

- 未来UPS技术趋势:无变压器技术解析(08-26)

- 12位串行A/D转换器MAX187的应用(10-06)

- AGC中频放大器设计(下)(10-07)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)