基于DDS芯片AD9852的雷达回波模拟器设计

在I/O缓冲区中,只有提供更新信号,这些数据才会更新到程序寄存器。AD9852提供内部更新和外部更新两种更新方式。内部更新通过更新时钟计数器完成,当计数器计自减为零后会产生一个内部更新信号;外部更新需要在外部更新管脚上给予一个高电平脉冲。默认的更新模式为内部更新,可以通过设置控制寄存器0x1F的0位进行修改。

3 系统设计

3.1 系统组成

3.2 工作原理

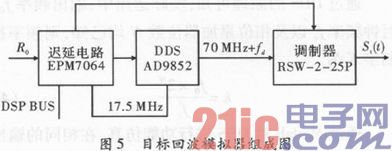

如图5所示,17.5 MHz基准信号经直接数字频率合成器(DDS,采用AD9852)输出70 MHz+fd的目标回波模拟信号,输出经脉冲调制器(采用MINI公司RSW-2-25P)形成目标回波信号St(t)。控制DSP通过总线(BUS)设置回波信号的迟延和DDS输出信号的多普勒频率。

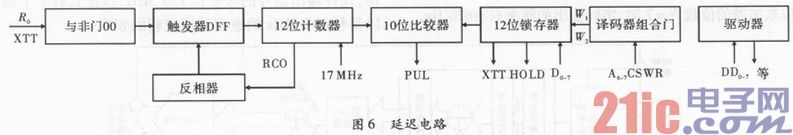

迟延电路组成如图6所示。XTT=1时电路正常工作,距离同步基准信号R0的前沿使触发器DFF翻转,输出高电平信号令12位计数器退出清零状态开始对17 MHz时钟计数。计数值的高10位(T0-9)与10位迟延时间锁存器的值DE0-9进行比较,二者相等时输出宽度为0.228 6μs的负脉冲PUL。计数器的进位信号RCO经反相后使触发器复位。译码器对输入的A6、A7、CS、WR信号译码,产生锁存器的数据锁存信号W0、W1。XTT信号为0时,电路关闭,无PUL信号输出。HOLD供AD9852使用,同时对数据总线信号D0-7、WR、RD进行驱动后供AD9852使用。

3.3 系统参数

距离迟延范围为0.23~233.8μs;fd频率范围:+400 kHz;频率分辨为5 Hz;衰减控制范围为>70 dB。

3.4 DDS芯片的优缺点

DDS芯片的优点主要体现在:输出频率相对、带宽较宽频率转换时间短、频率分辨率极高、相位变化连续等。输出频率带宽为采样频率的50%。DDS是一个开环系统,无任何反馈环节,这使得DDS的频率转换时间极短。若时钟的频率不变,DDS的频率分辨率就是由相位累加器的位数N决定。只要增加相位累加器的位数N即可获得任意小的频率分辨率。改变DDS输出频率,实际上改变的每一个时钟周期的相位增量,相位函数的曲线是连续的,只是在改变频率的瞬间其频率发生了突变,因而保持了信号相位的连续性。

另外,只要在DDS的波形存储器存放不同波形数据,就可以实现各种波形输出,如三角波、锯齿波和矩形波甚至是任意的波形。由于DDS中几乎所有部件都属于数字电路,易于集成、功耗低、体积小、重量轻、可靠性高,且易于程控,使用灵活,因此性价比较高。

DDS芯片存在的缺陷,主要表现在输出频带范围有限、输出杂散大。

由于DDS内部数模转换器(DAC)和波形存储器(ROM)的工作速度限制,使得DDS输出的最高频有限。由于DDS采用全数字结构,不可避免地引入了杂散。其来源主要有3个:相位累加器相位舍位误差造成的杂散;幅度量化误差造成的杂散和DAC非理想特性造成的杂散。

4 结束语

在DDS原理的基础上,提出了一种基于DDS芯片的雷达回波模拟器设计。该设计在实际运用中能够稳定地产生所需要的回波。而且,由于DDS芯片所具有的优点,使得其简单方便易于操作。随着低价格、高时钟频率、高性能的新一代DDS芯片问世,它将在更新领域得到更广泛的应用。

- 一种基于AD9857的信号发生器的设计(09-07)

- 基于FPGA及DDS技术的USM测试电源的设计 (09-08)

- 高性能双通道DDS芯片AD9958及其应用(02-04)

- 直接数字频率合成器DDS的优化设计(01-25)

- 如何预测直接数字频率合成器(DDS)输出频谱中主相位截断杂散的频率和幅度(06-18)

- 基于DDS的调频信号发生器的设计与仿真(04-12)