基于时钟输入和相位噪声的抖动计算应用

本文将采用低抖动时钟发生器AD9523为双通道、14位、250 MSPS ADC AD9643提供时钟。 使用这些产品后,常见的时钟频率为245.76 MHz,因此针对AD9523将采用30.72 MHz基准电压源(外部振荡器),并设置内部寄存器,以生成AD9643的低抖动时钟输出。根据时钟输入和相位噪声的抖动计算公式:

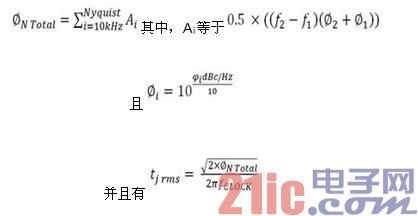

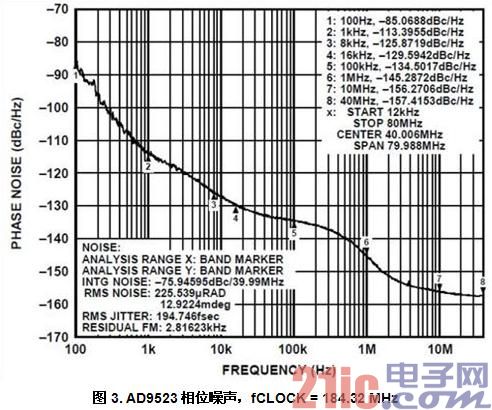

通过时钟源的抖动可以近似预测SNR的影响。 其中影响最大的是宽带相位噪声。 设计师可以利用AD9523在10 MHz失调到编码带宽(245.76 MHz)范围内的宽带相位噪声来预测ADC的SNR,如图1所示。

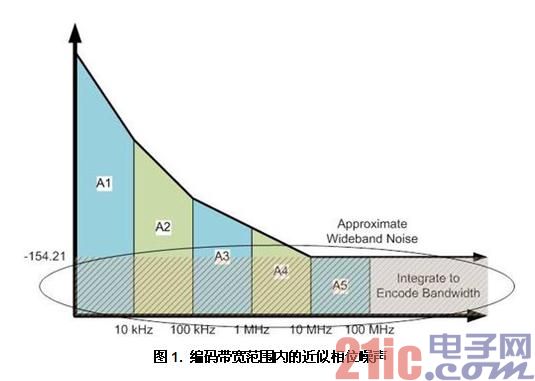

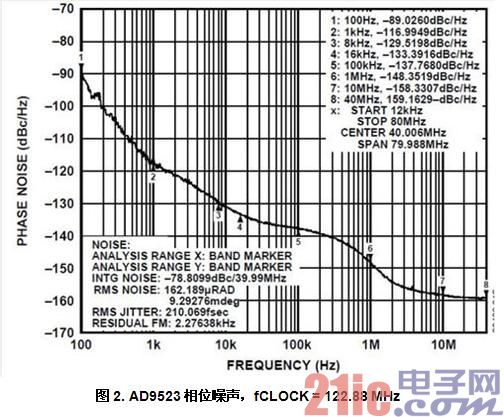

从AD9523中,复制并得到两种条件下产生的相位噪声曲线。第一种条件是输出时钟频率为122.88 MHz,第二种条件是输出时钟频率为184.32 MHz。现在,继续做另一次近似推测,而这次的项数较为宽松。使用这两条曲线中的数据执行线性插值运算,以便在输出时钟频率为245.76 MHz的情况下近似得到10 MHz失调的相位噪声。

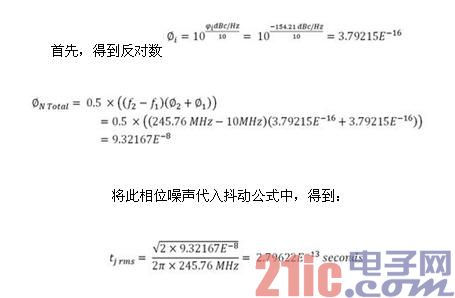

10 MHz失调时,若输出频率为122.88 MHz,则相位噪声为-158.3307 dBc/Hz。 类似地,若输出频率为184.32 MHz,则相位噪声为-156.2706 dBc/Hz。 执行线性插值运算,则输出频率为245.76 MHz时,10 MHz失调的预期相位噪声为-154.21 dBc/Hz(如图1所示)。 现在,利用等式近似计算面积,得到积分相位噪声。

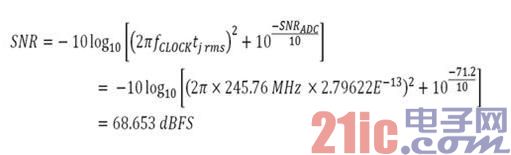

现在,通过计算得到了所有必须的要素,但依然缺少最后一个公式。 需要计算此抖动对AD9643的SNR产生的影响。 现在来看看这个公式是什么,然后代入已知数。已知时钟频率和rms抖动。 从AD9643数据手册中可以得到140 MHz模拟输入频率下的SNR等于71.4 dBFS。 使用公式,可以看到结果为:

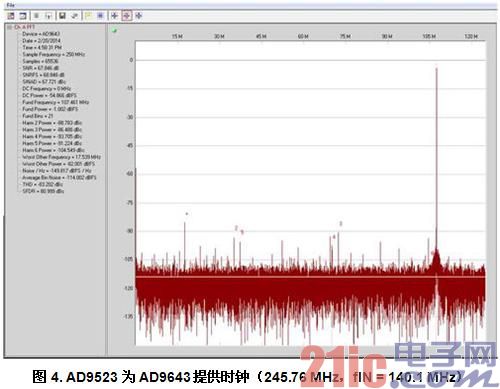

因此,当使用AD9523为AD9643提供时钟时,预期SNR值为68.763 dBFS。 最后,在实验室中进行设置,检查这些数字。

实验室结果显示SNR值为68.848 dBFS: 这是一个非常好的结果! 这一结果表明实际测量值非常接近预测的68.653 dBFS,并且可以看到预测结果与测量结果如此一致。

- 锁相环相位噪声与环路带宽的关系分析(08-04)

- 利用CyClockWizard实现时钟管理(03-28)

- 如何选择环路带宽平衡抖动、相位噪声、锁定时间或杂散(06-18)

- X波段多功能频率合成器设计(10-16)

- 锁相环相位噪声与环路带宽的关系分析(08-26)

- 12位串行A/D转换器MAX187的应用(10-06)