如何选择环路带宽平衡抖动、相位噪声、锁定时间或杂散

作为最重要的设计参数之一,选择环路带宽涉及到抖动、相位噪声、锁定时间或杂散之间的平衡。适合抖动的最优环路带宽BWJIT也是数据转换器时钟等许多时钟应用的最佳选择。如果BWJIT并非最佳选择,首先要做的仍是寻找最优环路带宽。

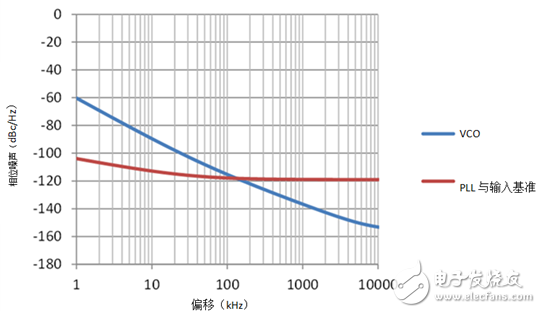

图1中,锁相环(PLL)与压控振荡器(VCO)噪声交叉处的偏移,BWJIT(约为140kHz)通过减少曲线下方的面积来优化抖动。

图1:最优抖动带宽

尽管此带宽BWJIT对抖动而言是最优的,但对于相位噪声、锁定时间或杂散却并非如此。表1给出了环路带宽对这些性能指标的影响的大致参考。

|

性能指标 |

最优带宽 |

备注 |

|

抖动 |

BWJIT |

最优值一般为BWJIT。在低集成限制更高的一些情况下,有时较窄的环路带宽实际上效果更好。 |

|

锁定时间 |

无限 |

VCO锁定时间随着环路带宽的增加而提高,但有时会受到VCO校准时间(用于集成VCO)的限制,或因VCO输入电容等寄生电容而使带宽无法增加。 |

|

杂散 |

0Hz |

一般而言环路带宽越窄,杂散越好,但有时会由环路滤波器周围来自主板或芯片上的串扰所主导。 |

|

相位噪声 |

0Hz或无限 |

如果相位噪声低于最优抖动带宽,相位噪声会随着带宽的变宽而增大,直到变成仅为输入基准和PLL造成的噪声。 如果相位噪声偏移大于最优抖动带宽,相位噪声会随着环路带宽的变窄而增大,直到变成仅为独立的VCO噪声。 |

表1:环路带宽对关键参数的影响

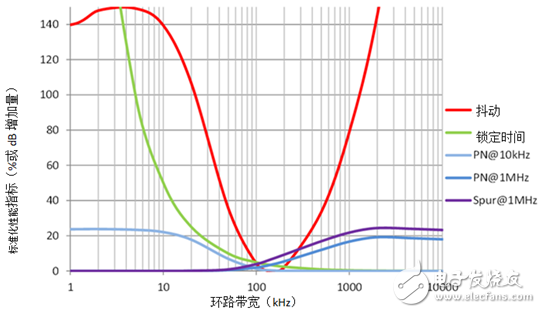

为了说明表1,图2中的模拟显示了变化的环路带宽的影响。锁定时间与抖动标准化指标为图2中从最小值增加的百分比。杂散与相位噪声指标为图2中从最小值增加的分贝。

图 2:环路带宽对标准化性能的影响

如图1所预测,环路带宽为140kHz左右时,最优抖动确实为最佳。环路带宽超出此范围会有利于锁定时间和10kHz相位噪声,但是会降低杂散和1MHz偏移的相位噪声。

因此,选择环路带宽的一种较好的方法是先选择最优抖动带宽(BWJIT),然后增加带宽提高锁定时间或低频偏相位噪声,或者降低带宽提高高频偏相位噪声或杂散。

- 锁相环相位噪声与环路带宽的关系分析(08-04)

- 锁相环相位噪声与环路带宽的关系分析(08-26)

- 利用CyClockWizard实现时钟管理(03-28)

- 基于时钟输入和相位噪声的抖动计算应用(10-16)

- X波段多功能频率合成器设计(10-16)