基于FinFET的SoC系统设计

时间:02-11

来源:互联网

点击:

大家都在谈论FinFET——可以说,这是MOSFET自1960年商用化以来晶体管最大的变革。几乎每个人——除了仍然热心于全耗尽绝缘体硅薄膜(FDSOI)的人,都认为20 nm节点以后,FinFET将成为SoC的未来。但是对于要使用这些SoC的系统开发人员而言,其未来会怎样呢?

回答这一问题最好的方法应该是说清楚FinFET对于模拟和数字电路设计人员以及SoC设计人员究竟意味着什么。从这些信息中,我们可以推断出FinFET在系统级意味着什么。

FinFET有什么不同?

关于FinFET及其结构 (图1) 理论的讨论已经有很多了,这里我们不再重复这些讨论。从电路设计人员的角度看,我们更关心FinFET究竟与平面MOSFET有什么不同。关于这一问题,今年的设计自动化大会(DAC)技术讨论专题为模拟设计人员开辟了新思路。

图1.FinFET经常出现在各种资料中

“采用FinFET进行模拟设计”而不是调侃的说“上帝一定疯了”,这代表了四个专家的观点:代工线代表TSMC的Eric Soenen,Globalfoundries的Richard Trihy、工具专家Synopsys的Navraj Nandra,以及设计经理Freescale的Scott Herrin。讨论集中在新晶体管的电气特性上。在赞成一方,Herrin指出,FinFET能够以很低的亚阈值泄漏电流实现高增益。

Nandra补充说,“FinFET固有增益很高,但是跨导(gm)实际上很低,和频率(ft)一样。更先进的几何布局比平面器件更容易实现匹配,能够很好的控制晶体管特性。结果是,您可以开发性能更好的电路。而且,还有其他的令人惊奇的地方。例如,输出电流较小,因此,您开发的数据转换器会更小。”

但是也有挑战。Nandra说,gm和gd较低,而栅极泄漏较大,栅极电容要比同样尺寸的平面器件大两倍。正如Soenen所指出的,大家都知道的一点是,FinFET栅极宽度是量化的:圆晶上的每一个晶体管都有相同的标称栅极宽度。因此,习惯于对每一晶体管采用w值的模拟设计人员只能并行采用一组同样的FinFET——实际上,w作为电路参数可以是连续变量,直至一组正整数。

布板问题

通过采用多个最小宽度晶体管来替代宽度可调晶体管,量化会改变布板习惯。Nanda说,例如,Synopsys有一款工具将栅极宽度比例转换为所需的翅片数。但是在另一讨论组的研讨中,Cadence硅片流程副总裁Anirudh Devgan提出了更严重的布板问题。

Devgan说:“采用更先进的几何布局后,多模式会更加复杂。随着复杂度的提高,很难预测设计规则错误。错误与环境相关。”

有些规则是熟悉的:例如,减小耦合的间隔规则,平板印刷的形状规则等。双模式增加了颜色规则,以保证最精细的模式能够分成两个独立的掩膜。还有相对较新的布板相关效应,Devgan指出了其中的六个——包括非常接近和多间隔等,这对晶体管行为有很大的影响。为说明问题的严重性,Devgan指出,在20 nm已经有5,000条布板规则需要进行检查。

对于模拟设计人员和数字单元库开发人员,这么复杂的结果是,几乎不可能开发DRC结构干净的布板。由于提取和DRC带来的布板问题,设计人员必须预测多次迭代。Devgan提醒说:“这需要几个星期的时间。40%的设计时间都花在收敛上。”

建模挑战

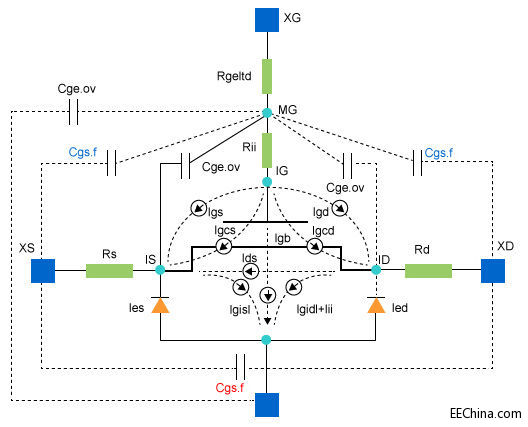

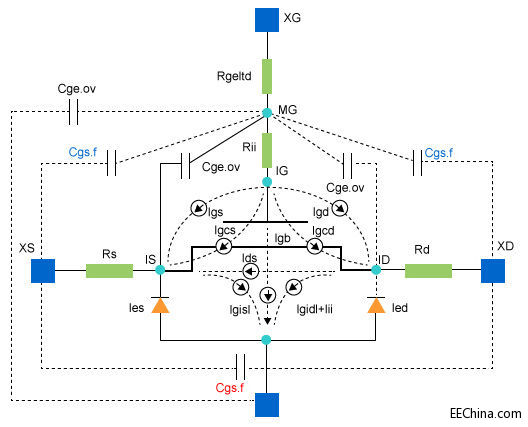

除了晶体管行为上的这些不同之外,电路设计人员在FinFET上还遇到了其他一些问题:仿真模型在结构上与平面MOSFET不同,会更复杂(图2)。Trihy提醒说,“如果您看一下模型,杂散电容的数量增加了十倍。还不清楚桌面驱动的仿真器能否处理FinFET。”

图2.FinFET仿真器模型会非常复杂

即使是如此复杂,也并不是所有模型在所有条件下都正确。因此,对于不熟悉平面晶体管的用户,模型选择会与电路相关,可能也会与布板相关。Herrin同意,“有不同点,您必须知道模型的局限性。

Nandra说,Synopsys一直结合使用SPICE和TCAD工艺模型,以及BSIM-4公共多栅极模型,以实现FinFET电路的精确仿真。他说,即使是在亚阈值区,BSIM-4也的确实现了精确的行为模型。但是,用在电路仿真时,模型会非常复杂。Nandra承认,“您必须采用结构相关的方法来解决杂散问题。”

Trihy继续这一主题。他问到,“器件模型会停在哪里,从哪里开始提取电路?采用FinFET电路,边界是模糊的。您可以依靠设计规则来限制交互,但是,最后,最重要的可能不是模型的精度,而是提取的精度。”Devgan在他一次发言中,提醒说,在某些情况下,可能需要现场解决问题,对复杂的紧密封装的3D结构进行精确的提取,FinFET电路会有这种结构。

新方法,新电路

晶体管行为、布板规则和建模方法出现了很大的变化,因此,适用于28 nm平面工艺的电路拓扑不太可能用在14 nm FinFET工艺上。量化会带来一些挑战。低电压、受限的gm以及大栅极电容会导致其他变化,包括,限制扇出,处理压缩动态范围等。Soenen提醒说,“这不是电源技术,但我们计划提供1.8 V FinFET。”Herrin解释说,例如,在嵌入式应用中,电压限制意味着完全不同的ESD电路,采用新方法来支持高电压I/O。

Soenen和Nandra同意这些变化带来的影响。Soenen预测说:“您会在模拟电路中看到很多数字辅助内容。会看到开关电容滤波器,更多的使用过采样技术。”

Nandra补充说,“我们看到了FinFET之前还没有的电路。”

回答这一问题最好的方法应该是说清楚FinFET对于模拟和数字电路设计人员以及SoC设计人员究竟意味着什么。从这些信息中,我们可以推断出FinFET在系统级意味着什么。

FinFET有什么不同?

关于FinFET及其结构 (图1) 理论的讨论已经有很多了,这里我们不再重复这些讨论。从电路设计人员的角度看,我们更关心FinFET究竟与平面MOSFET有什么不同。关于这一问题,今年的设计自动化大会(DAC)技术讨论专题为模拟设计人员开辟了新思路。

图1.FinFET经常出现在各种资料中

“采用FinFET进行模拟设计”而不是调侃的说“上帝一定疯了”,这代表了四个专家的观点:代工线代表TSMC的Eric Soenen,Globalfoundries的Richard Trihy、工具专家Synopsys的Navraj Nandra,以及设计经理Freescale的Scott Herrin。讨论集中在新晶体管的电气特性上。在赞成一方,Herrin指出,FinFET能够以很低的亚阈值泄漏电流实现高增益。

Nandra补充说,“FinFET固有增益很高,但是跨导(gm)实际上很低,和频率(ft)一样。更先进的几何布局比平面器件更容易实现匹配,能够很好的控制晶体管特性。结果是,您可以开发性能更好的电路。而且,还有其他的令人惊奇的地方。例如,输出电流较小,因此,您开发的数据转换器会更小。”

但是也有挑战。Nandra说,gm和gd较低,而栅极泄漏较大,栅极电容要比同样尺寸的平面器件大两倍。正如Soenen所指出的,大家都知道的一点是,FinFET栅极宽度是量化的:圆晶上的每一个晶体管都有相同的标称栅极宽度。因此,习惯于对每一晶体管采用w值的模拟设计人员只能并行采用一组同样的FinFET——实际上,w作为电路参数可以是连续变量,直至一组正整数。

布板问题

通过采用多个最小宽度晶体管来替代宽度可调晶体管,量化会改变布板习惯。Nanda说,例如,Synopsys有一款工具将栅极宽度比例转换为所需的翅片数。但是在另一讨论组的研讨中,Cadence硅片流程副总裁Anirudh Devgan提出了更严重的布板问题。

Devgan说:“采用更先进的几何布局后,多模式会更加复杂。随着复杂度的提高,很难预测设计规则错误。错误与环境相关。”

有些规则是熟悉的:例如,减小耦合的间隔规则,平板印刷的形状规则等。双模式增加了颜色规则,以保证最精细的模式能够分成两个独立的掩膜。还有相对较新的布板相关效应,Devgan指出了其中的六个——包括非常接近和多间隔等,这对晶体管行为有很大的影响。为说明问题的严重性,Devgan指出,在20 nm已经有5,000条布板规则需要进行检查。

对于模拟设计人员和数字单元库开发人员,这么复杂的结果是,几乎不可能开发DRC结构干净的布板。由于提取和DRC带来的布板问题,设计人员必须预测多次迭代。Devgan提醒说:“这需要几个星期的时间。40%的设计时间都花在收敛上。”

建模挑战

除了晶体管行为上的这些不同之外,电路设计人员在FinFET上还遇到了其他一些问题:仿真模型在结构上与平面MOSFET不同,会更复杂(图2)。Trihy提醒说,“如果您看一下模型,杂散电容的数量增加了十倍。还不清楚桌面驱动的仿真器能否处理FinFET。”

图2.FinFET仿真器模型会非常复杂

即使是如此复杂,也并不是所有模型在所有条件下都正确。因此,对于不熟悉平面晶体管的用户,模型选择会与电路相关,可能也会与布板相关。Herrin同意,“有不同点,您必须知道模型的局限性。

Nandra说,Synopsys一直结合使用SPICE和TCAD工艺模型,以及BSIM-4公共多栅极模型,以实现FinFET电路的精确仿真。他说,即使是在亚阈值区,BSIM-4也的确实现了精确的行为模型。但是,用在电路仿真时,模型会非常复杂。Nandra承认,“您必须采用结构相关的方法来解决杂散问题。”

Trihy继续这一主题。他问到,“器件模型会停在哪里,从哪里开始提取电路?采用FinFET电路,边界是模糊的。您可以依靠设计规则来限制交互,但是,最后,最重要的可能不是模型的精度,而是提取的精度。”Devgan在他一次发言中,提醒说,在某些情况下,可能需要现场解决问题,对复杂的紧密封装的3D结构进行精确的提取,FinFET电路会有这种结构。

新方法,新电路

晶体管行为、布板规则和建模方法出现了很大的变化,因此,适用于28 nm平面工艺的电路拓扑不太可能用在14 nm FinFET工艺上。量化会带来一些挑战。低电压、受限的gm以及大栅极电容会导致其他变化,包括,限制扇出,处理压缩动态范围等。Soenen提醒说,“这不是电源技术,但我们计划提供1.8 V FinFET。”Herrin解释说,例如,在嵌入式应用中,电压限制意味着完全不同的ESD电路,采用新方法来支持高电压I/O。

Soenen和Nandra同意这些变化带来的影响。Soenen预测说:“您会在模拟电路中看到很多数字辅助内容。会看到开关电容滤波器,更多的使用过采样技术。”

Nandra补充说,“我们看到了FinFET之前还没有的电路。”

MOSFET SoC 电路 自动化 DAC Freescale 电流 电容 Cadence 仿真 PIC 电压 嵌入式 模拟电路 滤波器 相关文章:

- 如何提升数字控制电源性能?MOSFET驱动器有办法(10-25)

- 基于单片机的脉冲快速充电系统设计(06-08)

- 硅光子带来新的设计挑战(07-07)

- 怎么能使Simulink的仿真速度更快?(08-19)

- IoT促进了低功耗的发展(12-05)

- 运用互补性显微术在终极尺度上三维重构并分析同一个纳米级样品(04-29)