Veloce仿真环境下的SoC端到端软硬件功能验证

时间:07-18

来源:互联网

点击:

很多人认为硬件加速器无非是一种速度更快的仿真器而已。毫无疑问,由于硬件加速器使用物理硬件进行仿真,使用硬件加速器验证复杂的集成电路和大型片上系统(SoC)能比软件仿真器快若干数量级。与仿真用通用计算机相比,仿真用单一功能计算机能提供更高容量、更高效的系统。

并且,许多拥有并使用硬件加速器的公司都发现,除具有加快仿真速度的功能外,硬件加速器还具有其他一些功能。例如,许多经验丰富的硬件加速器用户正在推动完整的端到端功能验证的封装,即待测设计的一端为驱动程序,另一端为其他目标外围设备。端到端功能测试能实现在流片前确认大型SoC(包含如多媒体、PCIe、USB和以太网)的完整功能路径。

与单纯地加快仿真速度相比,能够充分验证驱动程序和硬件则有更显著的价值。由于在硬件加速器上使用真实的驱动程序和精确的硬件外围接口来进行调试,这给片上系统(SoC)的可用性带来更多的保证。同时,经过全面测试的设备驱动程序能加快回片后的调试进度。

此外,硬件加速器的高速度和大容量使得待测设计(DUT)可以运行于和流片后一样的硅芯片原生环境上,远远早于FPGA原型和样片。硬件加速器使启动实时操作系统(RTOS)、运行设备驱动程序、执行复杂的计算、发送指令到DUT并显示结果成为可能。如此一来,硬件加速器用户所能做的远多于仿真加速,他们现在可以在硅的环境中验证一个“虚拟”的SoC,完成和真实芯片一样的测试。

用户已成功地应用这种端到端验证流程的其中一个领域就是验证手机的图形处理单元(GPU)。首先,在硬件加速器中对GPU核进行编译。然后,调用驱动程序。而为了运行驱动程序,必须启动RTOS,因为设备驱动程序需要借助RTOS中包含的功能才能运行。最后,GPU对图像进行渲染,换句话说,就是DUT的输出。整个过程中会涉及到一系列非常复杂的操作。启动LinuxRTOS需要数十亿时钟周期。RTOS将一张原始图像发送至设备驱动程序。设备驱动程序首先对图像进行无数次计算和存储操作,然后获取和向GPU提供存储地址等信息,最后指示GPU对图像进行渲染。然后,GPU从这些地址中获取所需的数据,以便进行图片制作。所有这些活动都需要运行大量的软件,而且需要数十亿个周期将一系列帧转变成视频。

如此巨大的时钟周期数,软件仿真器是无法简单完成的,而硬件加速器可以。例如,Mentor Graphics的Veloce硬件加速器可每秒运行一百万个周期,所以用户可在约两个小时内就能运行一百亿个周期。能够在处理器上运行驱动程序,接收原始图像,对图像进行准备,将图像发送至GPU进行渲染,然后处理成最终图像,这些使得硬件加速器用户能够如同测试最终产品一样充分测试待测设计。

Veloce的用户还拥有一个独特的优势,就是使用运行于工作站上的VirtuaLAB多媒体分析组件将GPU渲染的图像显示出来,该组件可从硬件加速器中获取多个帧并组合成视频。这使得Veloce用户能够看到实时视频,所以用户就可以直观地检查是否存在响应时间慢、抖动、拖尾、重影等现象。

图1: VirtuaLAB多媒体分析组件从运行于Veloce硬件加速器的待测设计中收集视频和音频流并对其进行分析和可视化。

只有Mentor Graphics的Veloce仿真环境可以提供这样一个端到端功能验证流程,因为只有Veloce具有这种流程要求的配套技术。Veloce提供了一个完整的功能验证环境,包括断言、功能覆盖、低功耗验证、全面的嵌入式软件调试套件、虚拟和物理外设、虚拟探针、加速软件执行、快速、准确的设计编译、全芯片调试可视性和企业级服务器功能。 Mentor无与伦比的超高速数据通道能以闪电般的速度实现仿真器和工作站之间大量数据的传输,因此工程师可以在不中断仿真运行的前提下在硬件加速器和工作站上进行调试。

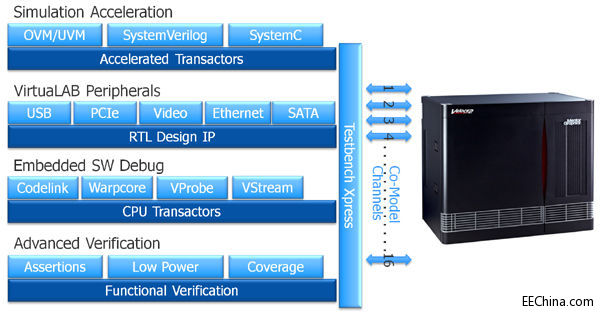

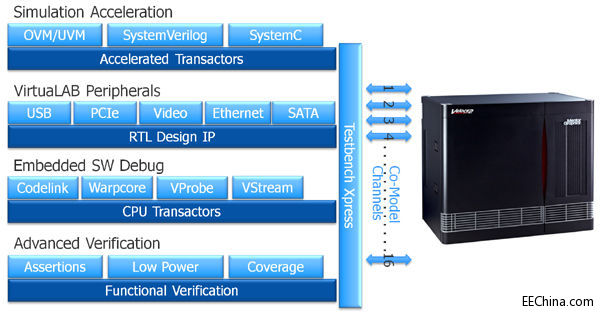

图2:硬件加速技术正变得不仅仅是加速仿真速度。

由于结合了驱动程序、RTOS和GPU,基于硬件加速器的端到端SoC功能验证流程为用户提供了很高的信心,正因为进行了全面的功能验证,前述芯片的视频接口、处理器和存储子系统出现功能错误的可能性很小。并且由于驱动程序已经在硬件加速器实现的真实硬件上进行过充分调试,所以一旦芯片出现任何问题,设计团队就会知道芯片存在制造方面的问题,因此不需要浪费时间在重新验证GPU或GPU与处理器的接口上,从而大大提高流片信心和产品上市速度。

并且,许多拥有并使用硬件加速器的公司都发现,除具有加快仿真速度的功能外,硬件加速器还具有其他一些功能。例如,许多经验丰富的硬件加速器用户正在推动完整的端到端功能验证的封装,即待测设计的一端为驱动程序,另一端为其他目标外围设备。端到端功能测试能实现在流片前确认大型SoC(包含如多媒体、PCIe、USB和以太网)的完整功能路径。

与单纯地加快仿真速度相比,能够充分验证驱动程序和硬件则有更显著的价值。由于在硬件加速器上使用真实的驱动程序和精确的硬件外围接口来进行调试,这给片上系统(SoC)的可用性带来更多的保证。同时,经过全面测试的设备驱动程序能加快回片后的调试进度。

此外,硬件加速器的高速度和大容量使得待测设计(DUT)可以运行于和流片后一样的硅芯片原生环境上,远远早于FPGA原型和样片。硬件加速器使启动实时操作系统(RTOS)、运行设备驱动程序、执行复杂的计算、发送指令到DUT并显示结果成为可能。如此一来,硬件加速器用户所能做的远多于仿真加速,他们现在可以在硅的环境中验证一个“虚拟”的SoC,完成和真实芯片一样的测试。

用户已成功地应用这种端到端验证流程的其中一个领域就是验证手机的图形处理单元(GPU)。首先,在硬件加速器中对GPU核进行编译。然后,调用驱动程序。而为了运行驱动程序,必须启动RTOS,因为设备驱动程序需要借助RTOS中包含的功能才能运行。最后,GPU对图像进行渲染,换句话说,就是DUT的输出。整个过程中会涉及到一系列非常复杂的操作。启动LinuxRTOS需要数十亿时钟周期。RTOS将一张原始图像发送至设备驱动程序。设备驱动程序首先对图像进行无数次计算和存储操作,然后获取和向GPU提供存储地址等信息,最后指示GPU对图像进行渲染。然后,GPU从这些地址中获取所需的数据,以便进行图片制作。所有这些活动都需要运行大量的软件,而且需要数十亿个周期将一系列帧转变成视频。

如此巨大的时钟周期数,软件仿真器是无法简单完成的,而硬件加速器可以。例如,Mentor Graphics的Veloce硬件加速器可每秒运行一百万个周期,所以用户可在约两个小时内就能运行一百亿个周期。能够在处理器上运行驱动程序,接收原始图像,对图像进行准备,将图像发送至GPU进行渲染,然后处理成最终图像,这些使得硬件加速器用户能够如同测试最终产品一样充分测试待测设计。

Veloce的用户还拥有一个独特的优势,就是使用运行于工作站上的VirtuaLAB多媒体分析组件将GPU渲染的图像显示出来,该组件可从硬件加速器中获取多个帧并组合成视频。这使得Veloce用户能够看到实时视频,所以用户就可以直观地检查是否存在响应时间慢、抖动、拖尾、重影等现象。

图1: VirtuaLAB多媒体分析组件从运行于Veloce硬件加速器的待测设计中收集视频和音频流并对其进行分析和可视化。

只有Mentor Graphics的Veloce仿真环境可以提供这样一个端到端功能验证流程,因为只有Veloce具有这种流程要求的配套技术。Veloce提供了一个完整的功能验证环境,包括断言、功能覆盖、低功耗验证、全面的嵌入式软件调试套件、虚拟和物理外设、虚拟探针、加速软件执行、快速、准确的设计编译、全芯片调试可视性和企业级服务器功能。 Mentor无与伦比的超高速数据通道能以闪电般的速度实现仿真器和工作站之间大量数据的传输,因此工程师可以在不中断仿真运行的前提下在硬件加速器和工作站上进行调试。

图2:硬件加速技术正变得不仅仅是加速仿真速度。

由于结合了驱动程序、RTOS和GPU,基于硬件加速器的端到端SoC功能验证流程为用户提供了很高的信心,正因为进行了全面的功能验证,前述芯片的视频接口、处理器和存储子系统出现功能错误的可能性很小。并且由于驱动程序已经在硬件加速器实现的真实硬件上进行过充分调试,所以一旦芯片出现任何问题,设计团队就会知道芯片存在制造方面的问题,因此不需要浪费时间在重新验证GPU或GPU与处理器的接口上,从而大大提高流片信心和产品上市速度。

仿真 集成电路 SoC USB FPGA Linux Mentor 嵌入式 相关文章:

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 数字频率合成器的FPGA实现(08-07)

- 基于DSP的导弹仿真器嵌入式组件设计(04-30)

- 如何将DSP和MCU两者完美结合(08-10)

- 高性能仿真器与开发包加速普及DSP应用开发(11-22)

- 基于DSP内嵌PCI总线的卫星信号仿真器设计(04-17)