FPGA 原型设计:软件最重要!

时间:03-21

来源:互联网

点击:

FPGA 原型设计人员艰苦努力所得的明显回报就是 ASIC 设计可以及时而毫无问题地完成产品定案(tape-out)。不过,原型设计还有一点日益重要的优势,即 ASIC 或 SoC 中嵌入的软件在项目开发的早期阶段便可与实际速度硬件进行完美集成。

为什么软件团队要关注 FPGA 原型设计问题

独立的 EDA 分析师 Gary Smith 指出(见图 1),SoC 采用的CMOS工艺节点日益小型化,而且技术越来越复杂,因此软件组成部分已成为产品特色和开发焦点所在。进入市场的最新消费类器件多采用复杂的 SoC,其中包括众多嵌入式处理器和几十万甚至数百万行代码。Apple iPhone 就是一个很好的例子,它至少包含 3 个 ARM 处理器。加速产品上市进程对产品推出至关重要,在此情况下,怎么才能在 SoC 环境中进行软件验证呢?

SoC 开发团队越来越多地开始采用 FPGA 原型设计作为解决方案来进行验证并及时推出各种类型的产品。

为什么选择原型设计技术?

集成操作系统、应用和硬件非常复杂,会出现许多不可预见的软件问题。实际速度运行的 FPGA 原型设计能提供一个独特的环境,在关键的集成阶段节约数月之久的高强度软件测试工作。如果这款原型设计还要采用其它软件,要进行其它实验室测试,那么原型设计的优势会进一步体现出来,即便对客户接受度测试来说都是有益的。Synplicity 推出的 HAPS (高速 ASIC 原型设计系统)等现成的高质量 FPGA原型验证板基本解决了投放产品的时间问题,剩下的就是要考虑成本问题:

增加板的用量将找出更多错误

软件的潜在用户数量巨大,他们会随心所欲使用软件,难免不造成操作系统锁死,应用崩溃,或者做些软件工程师根本想象不到的事情。

何时进行原型设计

在 SoC 设计完成之前就进行调试显然是非常有利的。图 1 显示了大型 ASIC 项目各阶段中通常要特别注意的模拟、仿真和原型设计问题。我们可以看到,FPGA 原型设计最常用,因为项目在集成阶段需要确保高速和高容量。

我们不妨设想这样一种情况,软件集成问题的最佳解决方案需要修改硬件。举例来说,需要将占用大量周期的DSP算法提取出来,并用协处理器或定制的器件逻辑来代替。如果 SoC 已基本完成了产品定案,甚至已完成设计推出了样片才发现这一问题,那么不管修改错误对最终产品有什么好处,我们也不太可能考虑对器件进行必要的调整了。事实上,早期进行 FPGA 原型设计有助于及时进行设计调整。FPGA 原型设计技术使用越来越多,其原因之一就是在项目早期阶段可判断软/硬件的问题并权衡利弊(也请参见图 1)。

原型设计面临的挑战

实施 ASIC 的 FPGA 原型需要解决多种开发难题。令人惊讶的是,设计硬件本身并不是最具挑战性的问题。事实上,许多厂商都提供为满足特定目的而设计的 ASIC 原型板(如HAPS)。真正的挑战则在于如何实施 FPGA 设计方案。

分区和 I/O 处理

尽管目前最大的 FPGA 每个都能处理 200 多万个 ASIC 门,但众多 ASIC 设计的要求要大得多。这就要求对 SoC 的关键部分进行原型设计,或者设计方案必须在多个 FPGA上进行分区。但这会造成一些有趣的障碍,因为我们的整体目标是进行验证,因此分区时必须尽可能减少对 ASIC RTL 的变动。设计方案分区会造成人为的分界线,如果设计方案的内部总线或数据路径较宽,则会造成所需 I/O 引脚的数量爆炸性增长,进而引起 FPGA 引脚不足。即便采用最新型的 FPGA,每个 FPGA支持 1000个以上的I/O 引脚,也有不够用的时候。

我们可在同一 FPGA 引脚上先对多个信号进行多路复用,然后再在目标 FPGA 上进行多路分解工作,从而生成更多 I/O 资源。即便如此,我们还是不希望变动 ASIC RTL,因此要进行自动引脚多路复用。这肯定会产品性能造成一定的影响;但 FPGA 的I/O足够快,即便采用多路复用技术,仍能提供足够高的性能,确保复杂的嵌入式软件验证工作能够以实际速度进行。

不改变 RTL 就修改拓扑结构

凭借设计人员的智慧,通过一定的手动干预,我们可在一个以上的 FPGA 中复制子模块,从而减少 I/O 限制,降低互连需求。通过对 RTL 做进一步的专门化操作,如对低级门进行位切片(bit-slicing)或压缩(zipper)更多复杂模块(这些都不需要变动 RTL),可进一步降低 FPGA I/O 需求。

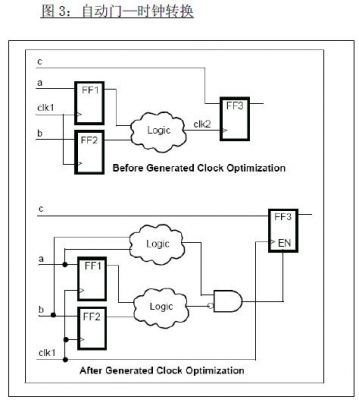

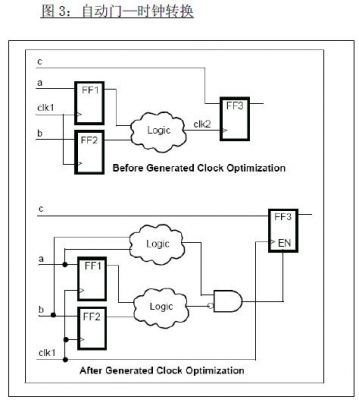

ASIC 时钟和 FPGA 时钟不一样将 SoC 设计移植到 FPGA 上时,设计团队还会面临更多问题,因为原始 RTL 的作者根本不可能考虑到 FPGA 问题。RTL 中不利于 FPGA 的因素包括 ASIC 元件例化和 RAM BIST 等,不过最重要的问题在于 IP 和时钟复杂性。为降低功耗,FPGA 会尽量支持ASIC 常用的门控时钟(gated-clock)设计风格。时钟门信号必须转化为 FPGA 硬件中的时钟启用(clock enables)信号。手动进行这种转换工作量太大并带来新的问题。一些合成工具可以自动进行门—时钟转换,甚至能支持复杂的时钟生成电路。图 3 显示了 Synplicity 的 Synplify Premier 中自动化时钟转化的实例。

为什么软件团队要关注 FPGA 原型设计问题

独立的 EDA 分析师 Gary Smith 指出(见图 1),SoC 采用的CMOS工艺节点日益小型化,而且技术越来越复杂,因此软件组成部分已成为产品特色和开发焦点所在。进入市场的最新消费类器件多采用复杂的 SoC,其中包括众多嵌入式处理器和几十万甚至数百万行代码。Apple iPhone 就是一个很好的例子,它至少包含 3 个 ARM 处理器。加速产品上市进程对产品推出至关重要,在此情况下,怎么才能在 SoC 环境中进行软件验证呢?

SoC 开发团队越来越多地开始采用 FPGA 原型设计作为解决方案来进行验证并及时推出各种类型的产品。

为什么选择原型设计技术?

集成操作系统、应用和硬件非常复杂,会出现许多不可预见的软件问题。实际速度运行的 FPGA 原型设计能提供一个独特的环境,在关键的集成阶段节约数月之久的高强度软件测试工作。如果这款原型设计还要采用其它软件,要进行其它实验室测试,那么原型设计的优势会进一步体现出来,即便对客户接受度测试来说都是有益的。Synplicity 推出的 HAPS (高速 ASIC 原型设计系统)等现成的高质量 FPGA原型验证板基本解决了投放产品的时间问题,剩下的就是要考虑成本问题:

增加板的用量将找出更多错误

软件的潜在用户数量巨大,他们会随心所欲使用软件,难免不造成操作系统锁死,应用崩溃,或者做些软件工程师根本想象不到的事情。

何时进行原型设计

在 SoC 设计完成之前就进行调试显然是非常有利的。图 1 显示了大型 ASIC 项目各阶段中通常要特别注意的模拟、仿真和原型设计问题。我们可以看到,FPGA 原型设计最常用,因为项目在集成阶段需要确保高速和高容量。

我们不妨设想这样一种情况,软件集成问题的最佳解决方案需要修改硬件。举例来说,需要将占用大量周期的DSP算法提取出来,并用协处理器或定制的器件逻辑来代替。如果 SoC 已基本完成了产品定案,甚至已完成设计推出了样片才发现这一问题,那么不管修改错误对最终产品有什么好处,我们也不太可能考虑对器件进行必要的调整了。事实上,早期进行 FPGA 原型设计有助于及时进行设计调整。FPGA 原型设计技术使用越来越多,其原因之一就是在项目早期阶段可判断软/硬件的问题并权衡利弊(也请参见图 1)。

原型设计面临的挑战

实施 ASIC 的 FPGA 原型需要解决多种开发难题。令人惊讶的是,设计硬件本身并不是最具挑战性的问题。事实上,许多厂商都提供为满足特定目的而设计的 ASIC 原型板(如HAPS)。真正的挑战则在于如何实施 FPGA 设计方案。

分区和 I/O 处理

尽管目前最大的 FPGA 每个都能处理 200 多万个 ASIC 门,但众多 ASIC 设计的要求要大得多。这就要求对 SoC 的关键部分进行原型设计,或者设计方案必须在多个 FPGA上进行分区。但这会造成一些有趣的障碍,因为我们的整体目标是进行验证,因此分区时必须尽可能减少对 ASIC RTL 的变动。设计方案分区会造成人为的分界线,如果设计方案的内部总线或数据路径较宽,则会造成所需 I/O 引脚的数量爆炸性增长,进而引起 FPGA 引脚不足。即便采用最新型的 FPGA,每个 FPGA支持 1000个以上的I/O 引脚,也有不够用的时候。

我们可在同一 FPGA 引脚上先对多个信号进行多路复用,然后再在目标 FPGA 上进行多路分解工作,从而生成更多 I/O 资源。即便如此,我们还是不希望变动 ASIC RTL,因此要进行自动引脚多路复用。这肯定会产品性能造成一定的影响;但 FPGA 的I/O足够快,即便采用多路复用技术,仍能提供足够高的性能,确保复杂的嵌入式软件验证工作能够以实际速度进行。

不改变 RTL 就修改拓扑结构

凭借设计人员的智慧,通过一定的手动干预,我们可在一个以上的 FPGA 中复制子模块,从而减少 I/O 限制,降低互连需求。通过对 RTL 做进一步的专门化操作,如对低级门进行位切片(bit-slicing)或压缩(zipper)更多复杂模块(这些都不需要变动 RTL),可进一步降低 FPGA I/O 需求。

ASIC 时钟和 FPGA 时钟不一样将 SoC 设计移植到 FPGA 上时,设计团队还会面临更多问题,因为原始 RTL 的作者根本不可能考虑到 FPGA 问题。RTL 中不利于 FPGA 的因素包括 ASIC 元件例化和 RAM BIST 等,不过最重要的问题在于 IP 和时钟复杂性。为降低功耗,FPGA 会尽量支持ASIC 常用的门控时钟(gated-clock)设计风格。时钟门信号必须转化为 FPGA 硬件中的时钟启用(clock enables)信号。手动进行这种转换工作量太大并带来新的问题。一些合成工具可以自动进行门—时钟转换,甚至能支持复杂的时钟生成电路。图 3 显示了 Synplicity 的 Synplify Premier 中自动化时钟转化的实例。

FPGA SoC EDA CMOS 嵌入式 ARM 仿真 DSP 总线 电路 自动化 相关文章:

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)