例说FPGA连载16:电源电路设计

特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1c0nf6Qc

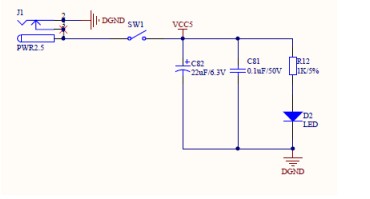

如图2.9所示,J1为FPGA的电源插座,SW1为电源开关,都是市面上最常见的元件,D2则是电源指示灯,当开关SW1闭合时,D2点亮,指示当前系统供电状态。

图2.9 FPGA电源插座电路

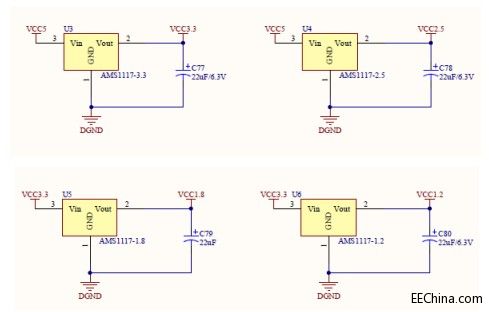

由于我们所选择的Cyclone IV系列FPGA器件整体功耗并不大,因此获得更好低纹波电源性能,如图2.10所示,我们使用了4颗LDO产生FPGA所需要的3.3V、2.5V、1.8V和1.2V这四档电压。

图2.10 FPGA四档电源电压产生电路

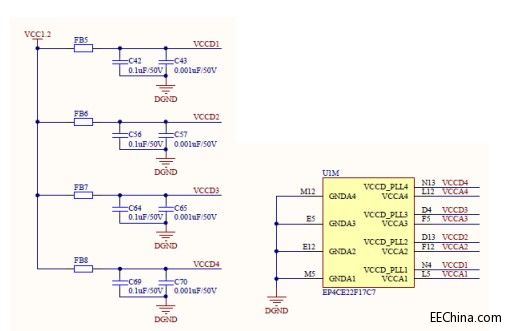

如图2.11所示,从Cyclone IV Device Handbook中可以查到,Cyclone IV系列器件的供电一般是分4大类,压值有3-4档(可能更多档,这主要取决于不同bank的I/O电压是否有特殊供电需求)。这4类电源分别是内核电压VCCINT、I/O电压VCCI/O、PLL模拟电压VCCA和PLL数字电压VCCD_PLL。这4类电源电压中,内核电压固定1.2V、PLL模拟电压固定2.5V、PLL数字电压固定1.2V;唯一不确定,或者说有选择余地的电源是I/O电压,它可以根据用户实际应用所需要的I/O标准选择不同的电压,我们的板子由于需要使用DDR2 SDRAM,它所连接的FPGA bank对应的I/O电压是1.8V,其他的bank都使用最常见的3.3V供电。

图2.11 Cyclone IV系列器件的供电标准

说到I/O电压,我们不得不多提两句,毕竟可以兼容非常多的I/O电压标准是FPGA的一大优势,尤其是各种高速差分信号的支持。图2.12中列出了我们这款器件支持的各种I/O电平标准。方形框出的3.3-V LVTTL和SSTL-18 Class I则是我们这款FPGA核心板中实际使用的I/O电平标准。

图2.12 Cyclone IV FPGA所支持的各种电平标准

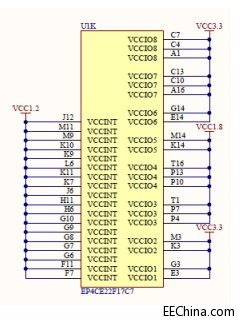

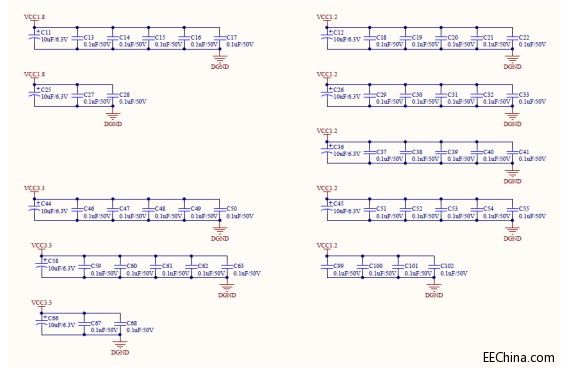

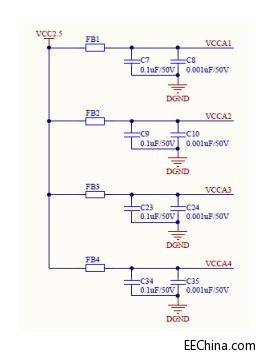

FPGA的供电电路如图2.13、图2.14所示。在FPGA的供电电路中,每1-2个电源引脚我们都配有1个去耦电容。当然了,在空间允许的情况下,每个电源引脚尽量都就近放置去耦电容。

图2.13 FPGA PLL供电电路

图2.14 FPGA I/O和核压供电电路

关于FPGA电源电路的PCB Layout设计,通常需要遵循以下的原则。

● 完整的或分割的电源层都应该就近与其对应的地层。

● 电源层和地层之间的绝缘层应该尽可能的薄,以增强耦合电容与平面电容(通常取3-4mil)。

● 为了最小化电感值,电源引脚应当就近直接连到相应的电源层。避免器件的电源引脚与供电源端或电源层之间的走线宽度过窄。板级设计者应该多参考电源芯片厂商提供的设计指南。

● 电源分割线的间距应该在25mil到100mil。

● 不同电源引脚不能够共用一个过孔。换句话说,每个电源引脚都应该至少有一个专用的过孔连接到电源层。

FPGA 电路 LDO 电压 电容 PCB 电感 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)