例说FPGA连载24:FX2(USB 2.0)外设子板设计

特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1c0nf6Qc

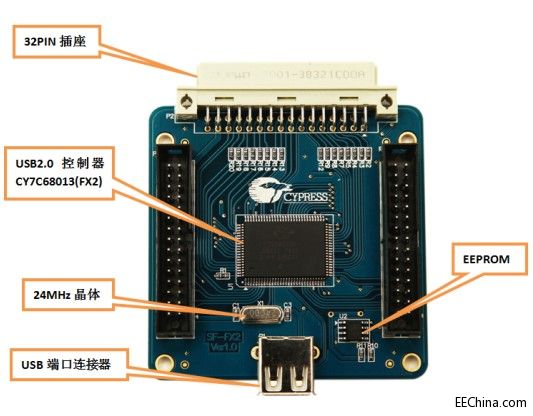

SF-FX2子板的实物照片如图2.41所示。

图2.41 SF-FX2子板实物照片

FX2(CY7C68013)是一款集成8051单片机的灵活的USB2.0控制器,其带宽可以接近USB2.0标称的480Mbps。

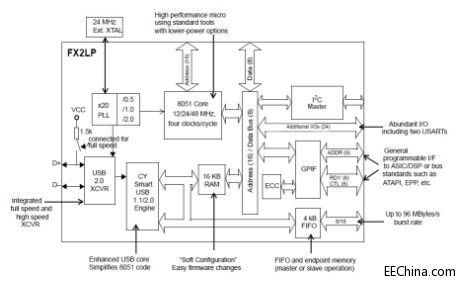

FX2的内部功能框图如图2.42所示。从图中不难看出,8051实际上并不直接参与USB数据的实际传输,而只是做一些基本的配置。从GPIF(或SlaveFIFO)接口传输的数据,在FX2内部传到了RAM中进行缓存,并且可以直接送到USB2.0的phy中传输给USB设备。

图2.42 FX2内部功能框图

SF-FX2子板和SF-VIP核心板需要进行连接的主要接口定义如表2.5所示。

表2.5 SF-FX2子板连接引脚定义

名称 | 位置 | 功能描述 |

SLCLK | P2-19 | FIFO读写时钟同步信号。 |

SLCS# | P2-16 | FIFO片选信号,低电平有效。 |

SLOE# | P2-14 | FIFO输出使能信号,低电平有效。 |

SLRD# | P2-26 | FIFO读使能信号,低电平有效。 |

SLWR# | P2-27 | FIFO写使能信号,低电平有效。 |

SLPKTEND# | P2-15 | FIFO包结束信号。 |

SLFLAGA | P2-13 | FIFO读空标志位,低电平有效。 |

SLD0 | P2-5 | FIFO数据总线。 |

SLD1 | P2-6 | FIFO数据总线。 |

SLD2 | P2-7 | FIFO数据总线。 |

SLD3 | P2-8 | FIFO数据总线。 |

SLD4 | P2-9 | FIFO数据总线。 |

SLD5 | P2-10 | FIFO数据总线。 |

SLD6 | P2-11 | FIFO数据总线。 |

SLD7 | P2-12 | FIFO数据总线。 |

SLD8 | P2-17 | FIFO数据总线。 |

SLD9 | P2-18 | FIFO数据总线。 |

SLD10 | P2-20 | FIFO数据总线。 |

SLD11 | P2-21 | FIFO数据总线。 |

SLD12 | P2-22 | FIFO数据总线。 |

SLD13 | P2-23 | FIFO数据总线。 |

SLD14 | P2-24 | FIFO数据总线。 |

SLD15 | P2-25 | FIFO数据总线。 |

SLA0 | P3-5 | FIFO地址。 |

SLA1 | P3-3 | FIFO地址。 |

SLFLAGB | P3-7 | FIFO写满标志位,低电平有效。 |

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)