FPGA研发之道(10)架构设计漫谈(五)数字电路的灵魂-流水线

时间:02-29

来源:互联网

点击:

流水线,最早为人熟知,起源于十九世纪初的福特汽车工厂,富有远见的福特,改变了那种人围着汽车转、负责各个环节的生产模式,转变成了流动的汽车组装线和固定操作的人员。于是,工厂的一头是不断输入的橡胶和钢铁,工厂的另一头则是一辆辆正在下线的汽车。这种改变,不但提升了效率,更是拉开了工业时代大生产的序幕。

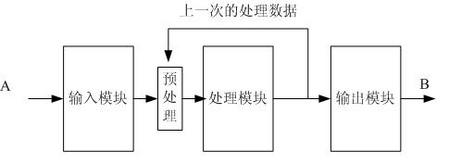

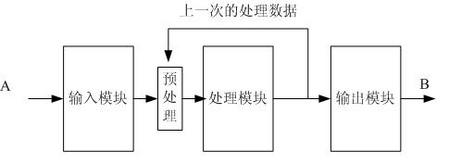

如今,这种模式常常应用于数字电路的设计之中,与现在流驱动的FPGA架构不谋而合。举例来说:某设计输入为A种数据流,而输出则是B种数据流,其流水架构如下所示:

每个模块只负责处理其中的一部分,这种处理的好处是,1、简化设计,每个模块只负责其中的一个功能,便于功能和模块划分。2,时序优化,流水的处理便于进行时序的优化,特别是处理复杂的逻辑,可以通过流水设计,改善关键路径,提升处理频率,并能提升处理性能。

各个流水线之间的连接方式也可通过多种方式,如果是处理的是数据块,流水模块之间可以通过FIFO或者RAM进行数据暂存的方式进行直接连接、也可以通过寄存器直接透传。也可通过某些支持brust传输的常用业界标准总线接口进行点对点的互联,例如AHB,WISHBONE,AVALON-ST等接口,这种设计的优点是标准化,便于模块基于标准接口复用。每个模块的接收接口为从接口(SLAVE),而发送接口为主接口(MASTER)。

架构流水的好处一目了然,但另一个问题,对于某些设计就需要谨慎处理,那就是时延。对于进入流水线的信息A,如果接入的流水处理的模块越多,其输出时的时延也越高,因此如对处理时延要要求的设计就需要在架构设计时,谨慎对待添加流水线。架构设计时,可以通过处理各个单元之间的延时估计,从而评估系统的时延,避免最终不能满足时延短的需求,返回来修改架构。

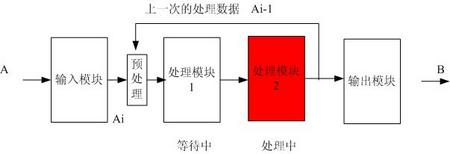

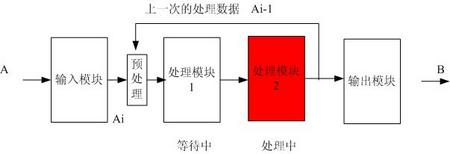

流水架构在另种设计中则无能为力,那就是带反馈的设计,如下图所示:

图中,需要处理模块的输入,需要上一次计算后的结果的值,也就是输出要反馈回设计的输入。例如某帧图像的解压需要解压所后的上一帧的值,才能计算得出。此时,流水的处理就不能使用,若强行添加流水,则输入需等待。

如上图中,如在需反馈的设计中强加流水,则输入信息Ai需要等待Ai-1处理完毕后,再进行输入,则处理模块1,就只能等待(空闲)。因此,问题出现了,流水线等待实际上就是其流水处理的的效果没有达到,白白浪费了逻辑和设计。

流水应用在调用式的设计中,可以通过接口与处理流水并行达到。即写入、处理、读出等操作可以做到流水式架构,从而增加处理的能力。

流水是FPGA架构设计中一种常用的手段,通过合理划分流水层次,简化设计,优化时序。同时流水在模块设计中也是一种常用的手段和技巧。这将在后续重陆续介绍。,流水本身简单易懂,而真正能在设计中活用,就需要对FPGA所处理的业务有着深刻的理解。正如那就话,知晓容易,践行不易,且行且珍惜。

如今,这种模式常常应用于数字电路的设计之中,与现在流驱动的FPGA架构不谋而合。举例来说:某设计输入为A种数据流,而输出则是B种数据流,其流水架构如下所示:

每个模块只负责处理其中的一部分,这种处理的好处是,1、简化设计,每个模块只负责其中的一个功能,便于功能和模块划分。2,时序优化,流水的处理便于进行时序的优化,特别是处理复杂的逻辑,可以通过流水设计,改善关键路径,提升处理频率,并能提升处理性能。

各个流水线之间的连接方式也可通过多种方式,如果是处理的是数据块,流水模块之间可以通过FIFO或者RAM进行数据暂存的方式进行直接连接、也可以通过寄存器直接透传。也可通过某些支持brust传输的常用业界标准总线接口进行点对点的互联,例如AHB,WISHBONE,AVALON-ST等接口,这种设计的优点是标准化,便于模块基于标准接口复用。每个模块的接收接口为从接口(SLAVE),而发送接口为主接口(MASTER)。

架构流水的好处一目了然,但另一个问题,对于某些设计就需要谨慎处理,那就是时延。对于进入流水线的信息A,如果接入的流水处理的模块越多,其输出时的时延也越高,因此如对处理时延要要求的设计就需要在架构设计时,谨慎对待添加流水线。架构设计时,可以通过处理各个单元之间的延时估计,从而评估系统的时延,避免最终不能满足时延短的需求,返回来修改架构。

流水架构在另种设计中则无能为力,那就是带反馈的设计,如下图所示:

图中,需要处理模块的输入,需要上一次计算后的结果的值,也就是输出要反馈回设计的输入。例如某帧图像的解压需要解压所后的上一帧的值,才能计算得出。此时,流水的处理就不能使用,若强行添加流水,则输入需等待。

如上图中,如在需反馈的设计中强加流水,则输入信息Ai需要等待Ai-1处理完毕后,再进行输入,则处理模块1,就只能等待(空闲)。因此,问题出现了,流水线等待实际上就是其流水处理的的效果没有达到,白白浪费了逻辑和设计。

流水应用在调用式的设计中,可以通过接口与处理流水并行达到。即写入、处理、读出等操作可以做到流水式架构,从而增加处理的能力。

流水是FPGA架构设计中一种常用的手段,通过合理划分流水层次,简化设计,优化时序。同时流水在模块设计中也是一种常用的手段和技巧。这将在后续重陆续介绍。,流水本身简单易懂,而真正能在设计中活用,就需要对FPGA所处理的业务有着深刻的理解。正如那就话,知晓容易,践行不易,且行且珍惜。

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- FPGA按键模式的研究与设计(03-24)

- 周立功:如何兼顾学习ARM与FPGA(05-23)