ISE时序约束笔记4——Global Timing Constraints

时间:02-19

来源:互联网

点击:

问题思考

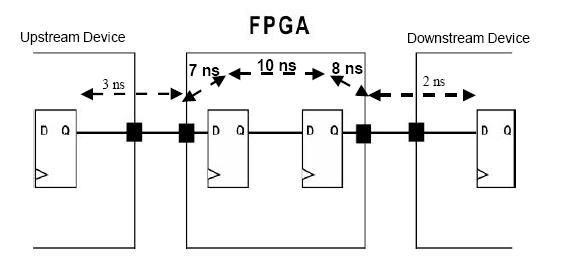

在这个电路中哪些路径是由OFFSET IN 和 OFFSET OUT来约束的?

问题解答:

——OFFSET IN:PADA to FLOP and PADB to RAM

——OFFSET OUT:LATCH to OUT1, LATCH to OUT2, and RAM to OUT1

问题思考

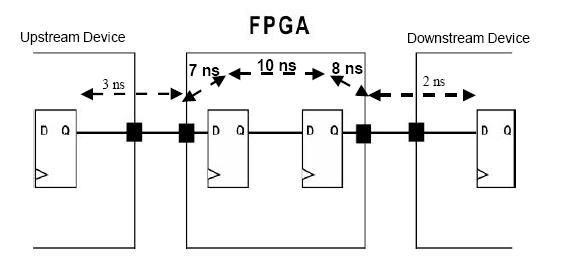

下面给出的系统框图里,你将给出什么样的约束值以使系统能够跑到100MHz?

——假设在下面的器件之间没有时钟偏斜

问题解答:

PERIOD = 10 ns , OFFSET IN (BEFORE) = 7 ns and OFFSET OUT (AFTER) = 8 ns

小结

1. 性能期望和时序约束相关联

2. 周期约束覆盖同步单元之间的延时路径

3. OFFSET约束覆盖从输入管脚到同步单元和从同步单元到输出管脚之间的延时路径

在这个电路中哪些路径是由OFFSET IN 和 OFFSET OUT来约束的?

问题解答:

——OFFSET IN:PADA to FLOP and PADB to RAM

——OFFSET OUT:LATCH to OUT1, LATCH to OUT2, and RAM to OUT1

问题思考

下面给出的系统框图里,你将给出什么样的约束值以使系统能够跑到100MHz?

——假设在下面的器件之间没有时钟偏斜

问题解答:

PERIOD = 10 ns , OFFSET IN (BEFORE) = 7 ns and OFFSET OUT (AFTER) = 8 ns

小结

1. 性能期望和时序约束相关联

2. 周期约束覆盖同步单元之间的延时路径

3. OFFSET约束覆盖从输入管脚到同步单元和从同步单元到输出管脚之间的延时路径

电路 相关文章:

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- FPGA按键模式的研究与设计(03-24)

- 周立功:如何兼顾学习ARM与FPGA(05-23)