Xilinx FPGA入门连载31:超声波测距回响脉宽计数之均值滤波处理

时间:12-03

来源:互联网

点击:

Xilinx FPGA入门连载31:超声波测距回响脉宽计数之均值滤波处理

特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1jGjAhEm

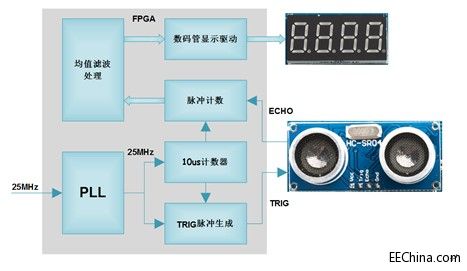

本例程基本的功能实现和前面一个例程一样,只是在原先的“脉冲计数”和“数码管显示驱动”两个功能块之间,增加了“均值滤波处理”功能的实现。

可能大家在上一个例程板级调试的时候已经注意到了,数码管显示的数据还是有些不够稳定,跳变比较快,也不是非常准确。所有“均值滤波处理”功能模块就是要来解决这些问题。

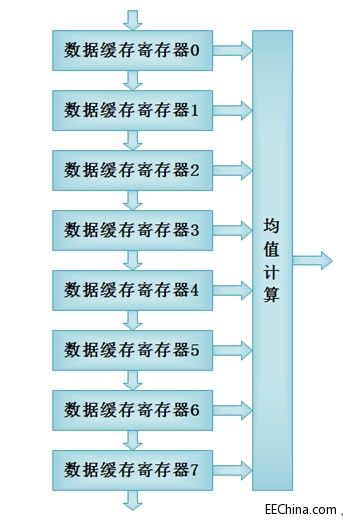

2 滤波算法与实现一般性的均值滤波,其算法都是“砍头、去尾、留中间”,即取一定的数据作为一组进行排序,剔除最大值和最大值,留下中间的数据进行求平均。

我们的算法要比这更简单一些。我们取每8个最新采集的数据,不做任何排序,直接求平均值。注意,每输入一个新的数据,就会相应的输出一个旧的数据,从而进行一组完全实时的最新的8个数据的均值计算。功能如图所示。

连接好下载线,给SP6开发板供电。

打开ISE,进入iMPACT下载界面,将本实例工程下的sp6.bit文件烧录到FPGA中在线运行。

此时我们在超声波测距模块前面摆放平整的障碍物,可以看到数码管上的16进制数据会发生变化。但是相对于上一个实例,这个实例的数码管显示数据要相对稳定一些。

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- 迄今为止最牛的ASIC验证平台(05-22)

- 验证FPGA设计:模拟,仿真,还是碰运气?(08-04)