Xilinx FPGA入门连载34:超声波测距终极结果显示之除法器IP解析

特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1jGjAhEm

在本例程的工程源码distance_compute.v中,例化了一个3个除法IP核。当然了,这3个除法IP核实际上配置完全一样,因此我们在IP核配置时,只要配置一遍即可。这里我们简单的来看看这个IP核是如何创建、配置并使用的。

2新建源文件打开ISE工程,如图所示,在“Design à Implementation à Hierarchy”中的任意位置单击鼠标右键,弹出菜单中选择“New Source..”。

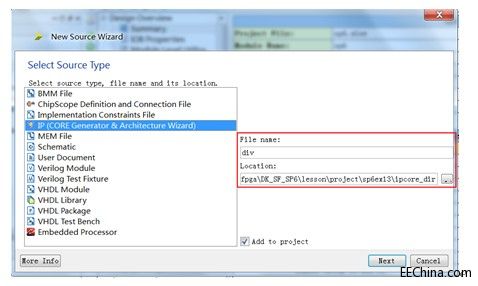

在“New Source Wizard”中,做如图所示的设置。

● “Select Source Type”中选择新建文件类型为“IP(CORE Generator & Architecture Wizard)”。

● “File name”即文件名,我们命名为“div”。

● “Location”下面输入这个新建文件所存放的路径,我们将其定位到工程路径下的“ipcore_dir”文件夹下。

● 勾选上“Add to project”。

完成以上设置后,点击“Next”进入下一步。

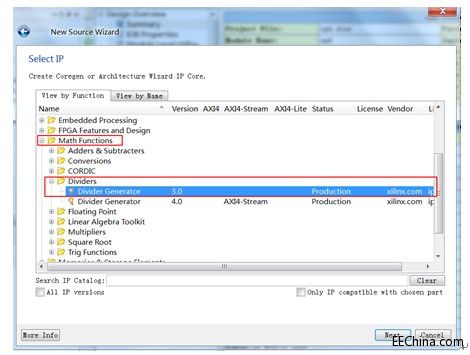

3IP选择在“Select IP”页面中,如图所示,我们在“Viewby Function”下面找到“Math Functions à Dividers à Divider Generator”,单击选中它,接着点击“Next”进入下一步。

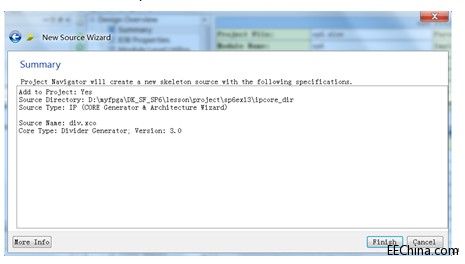

如图所示,弹出“Summary”页面后,点击“Finish”即可。

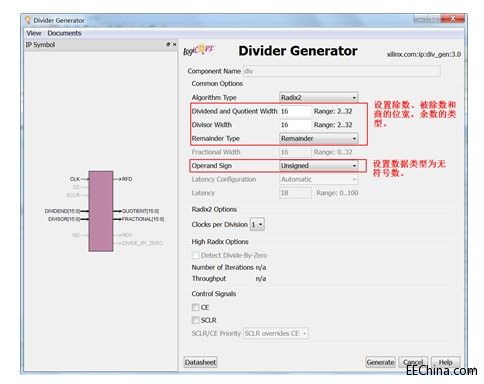

在Divider中,只有一个配置页面,如图所示。

● 被除数(dividend)、除数(divisor)和商(quotient)的位宽都设置为“16”。

● 余数(Remainder Type)的输出类型即余数(Remainder)。

● “Operand Sign”为无符号数(Unsigned)。

直接点击“Generate”生成配置好的IP核即可。

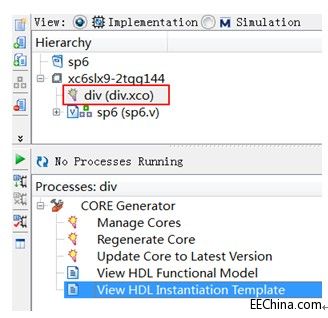

5例化模块“Generate”完成后,如图所示,我们可以在“Hierarchy”中选中div.xco即刚刚产生的IP核模块,然后双击打“Processes”下的“View HDLInstantiation Template”查看IP核的例化模板。

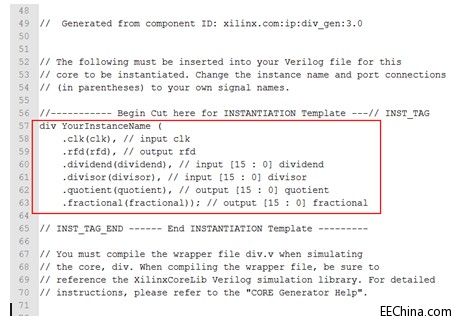

例化模板打开如图所示,矩形区域内的代码我们复制到工程源码中,对“( )”内的接口做好映射,就可以将其集成到我们的设计中。

如下代码所示,在我们的设计中,除法器被例化了3次,注意这里的3次例化,代表了实际上就有3个完全一样内部结构的乘法器实现在了设计中,而不是软件上函数调用的仅仅只有一个函数、只占用一个函数代码空间的情况。

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- 迄今为止最牛的ASIC验证平台(05-22)

- 验证FPGA设计:模拟,仿真,还是碰运气?(08-04)