Xilinx FPGA入门连载26:数码管驱动实例

特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1jGjAhEm

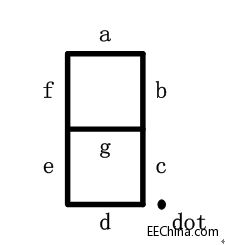

先来了解一下数码管的工作原理。如图所示,这是一个典型的带小数点的一位数码管。如果忽略小数点,我们通常称它为7段数码管(即便有小数点,我们也习惯的称呼为7段数码管),所谓7段,是指着7个发光二极管而言的。任意一个0-9的阿拉伯数字的显示,只要通过这7个发光二极管进行亮或灭的组合都可以实现。例如,我们要显示数字0,那么只要让发光二极管a、b、c、d、e、f点亮(g和dot熄灭)就可以了。

接下来,大家可能就要关心着这7个发光二极管是如何控制的,我们又是如何通过FPGA的I/O口去点亮或熄灭任意一个发光二极管?很简单,原理上来讲,一个带小数点的数码管的所有8个发光二极管的正极或负极有一个公共端,通常必须接GND(共阴极数码管)或者接VCC(共阳极数码管),而另一个非公共端的8个引脚就留给用户的I/O直接控制了。例如,如果我们使用的是共阴极的数码管,那么我们在使用该数码管时就要将其公共端接地(或者接低电平0),我们的应用中,把这个公共端连接到了FPGA的I/O脚上,这便是数码管的片选信号。如果FPGA的这个I/O脚输出低电平0,那么这个数码管就能够显示数字;如果这个I/O输出高电平1,那么无论数码管的8个段选端输出0还是1,都无法将8个发光二极管的任意一个点亮,这也达到了关闭数码管显示的效果。这样一来,这个数码管的公共端被我们当做了数码管片选引脚使用了,虽然不是名副其实的“片选”,但还真达到了异曲同工之妙。

我们的例程要实现的功能比较简单基础:让4个数码管每隔1s不断的递增计数显示,计数范围为0-F。为了便于代码编写控制7个用于段选(不包括小数点)的发光二极管显示不同的字符,这里只做了一个简单的对应表,把不同字符显示时的7个I/O值进行编码,如表所示。

| 数字/字符 | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

编码(16进制) | 3f | 06 | 5b | 4f | 66 | 6d | 7d | 07 |

数字/字符 | 8 | 9 | A | B | C | D | E | F |

编码(16进制) | 7f | 6f | 77 | 7c | 39 | 5e | 79 | 71 |

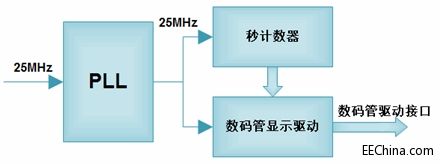

本实例的功能框图如图所示。PLL产生的25MHz时钟,分别供给两个子模块,秒计数器(counter.v)模块产生一个每秒递增的16位数据,这16位数据以16进制形式通过数码管显示驱动模块(seg7.v)显示到数码管上。数码管显示驱动模块以分时复用的片选方式,将数据送到数码管的各个段选位上。

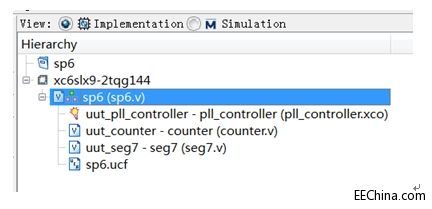

该实例工程的模块间层级关系如图所示。

将工程编译产生的sp6.bit文件下载到FPGA中。我们可以看到数码管从最低位开始依次从0到F(16进制形式)不断的递增。

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- 迄今为止最牛的ASIC验证平台(05-22)

- 验证FPGA设计:模拟,仿真,还是碰运气?(08-04)