基于FPGA的无损图像压缩系统设计

时间:11-10

来源:互联网

点击:

摘要:本文简要介绍了图像压缩的重要性和常用的无损图像压缩算法,分析了快速高效无损图像压缩算法(FELICS)的优势,随后详细分析了该算法的编码步骤和硬件实现方案,最后公布了基于该方案的FPGA性能指标。和其他压缩算法相比该方案可极大地减小无损图像压缩系统所需的存储空间和压缩时间。

引言

随着信息技术的巨大革新,数据存储和传输开始在人类生活中变得越来越重要,数据压缩技术因而应运而生,它不仅能减少数据存储所需的空间还可以缓解传输带宽的压力。数据压缩可以分为有损压缩和无损压缩两种,其中有损压缩技术可以获得较高的压缩比,但是会丢失一些图片信息,可以应用在对图像质量要求不高的领域,但是在医疗图像、航天图像等特殊领域中,则要求图像压缩算法是无损的[1]。

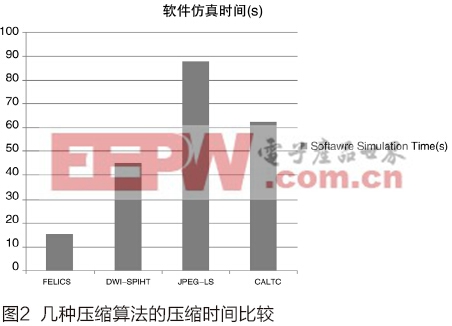

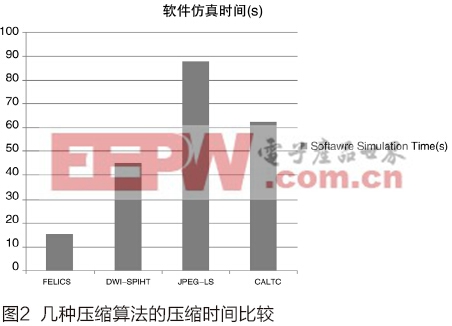

无损压缩技术可以去除冗余信息并保证重建的步骤不会对原始信息带来任何损失。这样一来,解码后的信息就和原始信息精确相等。CALIC [2]和JPEG-LS[3]等诸多算法都已经被广泛应用在这一领域。另外,离散小波变换(DWT)算法也常被用来放松对开环视频编码系统存储空间和带宽的要求。但是,这些算法大多对数据具有严重的依赖性并且编码步骤较为复杂,因此限制了其在高速产品中的应用。快速高效无损图像压缩系统(FELICS)于1993年由P.G.howard提出[4],这是一种以编码效率见长的无损图像压缩算法,并且编码时对数据没有依赖性,因此能应用在高速压缩系统中[5-6]。几种压缩算法的压缩比和压缩时间对比如图1所示,可以看出FELICS算法压缩比适中,但压缩效率的优势较为明显。

接下来将详细分析FELICS算法的优势和具体的编码步骤,最后将针对这一压缩算法提出一种基于FPGA的硬件实现方案。

1 整体算法设计

FELICS算法中应用到三种主要的技术手段:像素点分布模型的选取、修正的二元编码和GOLOMB-RICE熵编码。

1.1 像素点分布模型

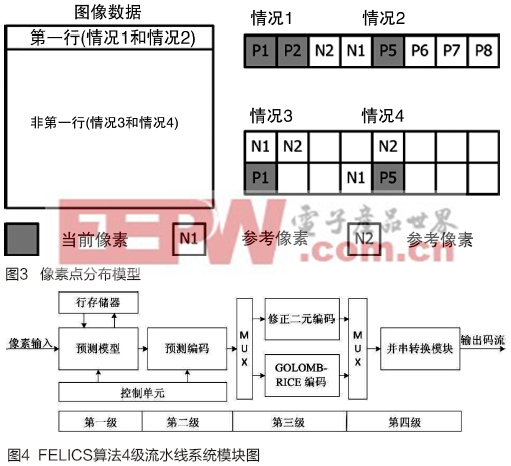

整幅图像前两个像素点不进行编码处理直接输出,从第三个像素点开始选取与之相邻的两个像素点作为参考像素点,参考像素点的选取规则如图3所示,用i和j来表示行号和列号,P,N1和N2表示当前像素点和两个参考像素点,选取规则如下:

If (i==1 && j2) N1=P[i,j-1],N2=P[i,j-2];

If (i>1 && j==1) N1=P[i-1,j],N2=P[i-1,j+1];

If (i>1 && j>1) N1=P[i,j-1],N2=P[i-1,j];

选出参考像素点N1与N2之后,将二者进行比较,记较大者为H,较小者为L,Δ为H-L。

依照当前像素点P位于区间[L,H]的位置信息,分为三种情况采用不同的编码方式:

If (L≤P≤H) 选用修正的二元编码,并用1比特’0’来表示P落于[L,H]内,残余值R=P-L;

If (P≤L) 选用GOLOMB-RICE编码,并用2比特’10’表示P落于小于下界L的区间内,残余值R=L-P-1;

If (H≤P) 同样选用GOLOMB-RICE编码,并用2比特’11’表示P落于大于上界H的区间内,残余值R=P-H-1。

1.2 修正的二元编码

在修正二元编码的编码区间[L,H]内,中间部分和两边部分相比,有像素点出现的概率要略高一些,所以对二进制编码进行修正,对中间部分像素点的残余值R赋予较短的编码,对两边部分像素点的残余值R赋予较长的编码。例如当△为5时,P值的可能值为0、1、2、3、4、5。在编码时,将处在区间中央的2、3分别编码为00和11,而将0、1、4、5分别编码为110、111、100和101。

1.3 GOLOMB-RICE熵编码

GOLOMB-RICE熵编码是GOLOMB编码的一种特殊情况,属于指数编码的一种。FELICS算法中像素点概率分布模型在小于下界L和大于上界H的部分是以指数形式分布的,符合GOLOMB-RICE编码的适用范围,因此选用这种编码方法。编码步骤如下:

(1)选定参数K

在整幅图像编码开始之前,建立一个U×V×T比特大小的累加表,其中U,V和T分别代表背景值Δ的个数、备选K值的个数和每一个K值下累计编码的长度。在每一次进行GOLOMB-RICE编码之前,按照Δ的数值定位到累加表的相应行,选出累计编码长度最短的K值作为当前像素残余值GOLOMB-RICE编码的K值。

(2)分别确定一进制和二进制编码

一进制编码:unary=R/2K的整数部分;

二进制编码:binary=R/2K的余数部分;

最终的GOLOMB-RICE编码由三部分组成:unary个’1’,binary的二进制形式和1比特’0’,其中’0’置于一进制编码和二进制编码之间,作为解码时的标志位。

(3)更新累加表

编码完成之后要依次用备选的K值对残余值R进行GOLOMB-RICE编码,计算出编码的长度并累加到累加表中K值相应的位置处,以用于后续像素点进行GOLOMB-RICE编码时K值的选取。

2 压缩系统硬件设计

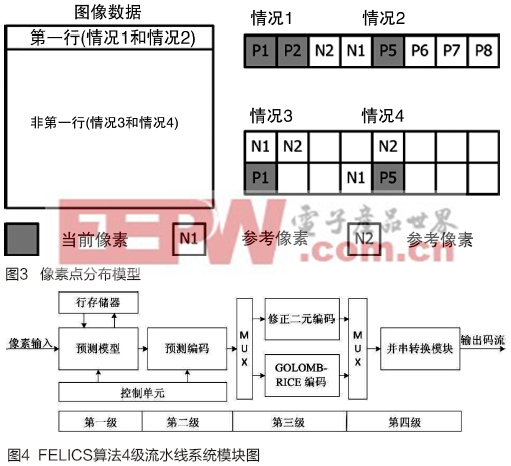

设计采用 4 级流水线结构,系统只有一个主时钟CLK作为工作时钟。硬件实现包括控制单元、上下文模型选取单元、预测单元、熵编码单元和并串转换单元,硬件结构框图如图 4。

控制单元负责产生控制信号以协调各电路模块的工作顺序;上下文模型选取单元将像素值输入存储器进行存储,产生当前像素、相邻像素和上下文预测值Δ;预测单元根据不同的上下文模型求出像素残余值;编码单元对像素残余值进行修正的二元编码或GOLOMB-RICE编码;并串转换单元负责将编码结果转换为码流进行输出。

图5所示为各个电路子模块的接口定义及连线图。其中上下文产生模块和预测模块功能具有连续性,用一个模块表示,像素值以光栅扫描的顺序逐行进行读入,需要一个行存储器对像素值进行存储,每完成对一个像素点的编码操作之后,将存储器中该处的像素值更新为当前行当前列的像素值,本方案处理的图像大小为512*512,因此只需要一个512*8比特的存储器。修正二元编码和GOLOMB-RICE编码模块算法相对复杂一些,为了加快系统的时钟频率,将算法中的计算步骤进行拆分细化。GOLOMB-RICE编码模块需要进行参数K的选取,若K的可能值有4个,则还需要256*8*4比特大小的存储器作为累加表。最后,由于编码后的码值是变长的,为了满足输出端口的要求,要对编码结果进行并串转换操作,输出端以码流的形式进行输出。

压缩系统已集成在XILINX VIRTEX-5 FPGA上,并利用开发板XUPV5_LX110T进行了验证,当工作频率为20MHZ时, 吞吐率可达45f/s,所需存储空间仅为13.1Kbits,每帧的功耗仅为13.67毫瓦。经过若干经典图像测试后发现此压缩系统的平均压缩比为2.2,和主流的无损图像压缩算法(如JPEG-LS)相当,但压缩效率提升约80%左右。

引言

随着信息技术的巨大革新,数据存储和传输开始在人类生活中变得越来越重要,数据压缩技术因而应运而生,它不仅能减少数据存储所需的空间还可以缓解传输带宽的压力。数据压缩可以分为有损压缩和无损压缩两种,其中有损压缩技术可以获得较高的压缩比,但是会丢失一些图片信息,可以应用在对图像质量要求不高的领域,但是在医疗图像、航天图像等特殊领域中,则要求图像压缩算法是无损的[1]。

无损压缩技术可以去除冗余信息并保证重建的步骤不会对原始信息带来任何损失。这样一来,解码后的信息就和原始信息精确相等。CALIC [2]和JPEG-LS[3]等诸多算法都已经被广泛应用在这一领域。另外,离散小波变换(DWT)算法也常被用来放松对开环视频编码系统存储空间和带宽的要求。但是,这些算法大多对数据具有严重的依赖性并且编码步骤较为复杂,因此限制了其在高速产品中的应用。快速高效无损图像压缩系统(FELICS)于1993年由P.G.howard提出[4],这是一种以编码效率见长的无损图像压缩算法,并且编码时对数据没有依赖性,因此能应用在高速压缩系统中[5-6]。几种压缩算法的压缩比和压缩时间对比如图1所示,可以看出FELICS算法压缩比适中,但压缩效率的优势较为明显。

接下来将详细分析FELICS算法的优势和具体的编码步骤,最后将针对这一压缩算法提出一种基于FPGA的硬件实现方案。

1 整体算法设计

FELICS算法中应用到三种主要的技术手段:像素点分布模型的选取、修正的二元编码和GOLOMB-RICE熵编码。

1.1 像素点分布模型

整幅图像前两个像素点不进行编码处理直接输出,从第三个像素点开始选取与之相邻的两个像素点作为参考像素点,参考像素点的选取规则如图3所示,用i和j来表示行号和列号,P,N1和N2表示当前像素点和两个参考像素点,选取规则如下:

If (i==1 && j2) N1=P[i,j-1],N2=P[i,j-2];

If (i>1 && j==1) N1=P[i-1,j],N2=P[i-1,j+1];

If (i>1 && j>1) N1=P[i,j-1],N2=P[i-1,j];

选出参考像素点N1与N2之后,将二者进行比较,记较大者为H,较小者为L,Δ为H-L。

依照当前像素点P位于区间[L,H]的位置信息,分为三种情况采用不同的编码方式:

If (L≤P≤H) 选用修正的二元编码,并用1比特’0’来表示P落于[L,H]内,残余值R=P-L;

If (P≤L) 选用GOLOMB-RICE编码,并用2比特’10’表示P落于小于下界L的区间内,残余值R=L-P-1;

If (H≤P) 同样选用GOLOMB-RICE编码,并用2比特’11’表示P落于大于上界H的区间内,残余值R=P-H-1。

1.2 修正的二元编码

在修正二元编码的编码区间[L,H]内,中间部分和两边部分相比,有像素点出现的概率要略高一些,所以对二进制编码进行修正,对中间部分像素点的残余值R赋予较短的编码,对两边部分像素点的残余值R赋予较长的编码。例如当△为5时,P值的可能值为0、1、2、3、4、5。在编码时,将处在区间中央的2、3分别编码为00和11,而将0、1、4、5分别编码为110、111、100和101。

1.3 GOLOMB-RICE熵编码

GOLOMB-RICE熵编码是GOLOMB编码的一种特殊情况,属于指数编码的一种。FELICS算法中像素点概率分布模型在小于下界L和大于上界H的部分是以指数形式分布的,符合GOLOMB-RICE编码的适用范围,因此选用这种编码方法。编码步骤如下:

(1)选定参数K

在整幅图像编码开始之前,建立一个U×V×T比特大小的累加表,其中U,V和T分别代表背景值Δ的个数、备选K值的个数和每一个K值下累计编码的长度。在每一次进行GOLOMB-RICE编码之前,按照Δ的数值定位到累加表的相应行,选出累计编码长度最短的K值作为当前像素残余值GOLOMB-RICE编码的K值。

(2)分别确定一进制和二进制编码

一进制编码:unary=R/2K的整数部分;

二进制编码:binary=R/2K的余数部分;

最终的GOLOMB-RICE编码由三部分组成:unary个’1’,binary的二进制形式和1比特’0’,其中’0’置于一进制编码和二进制编码之间,作为解码时的标志位。

(3)更新累加表

编码完成之后要依次用备选的K值对残余值R进行GOLOMB-RICE编码,计算出编码的长度并累加到累加表中K值相应的位置处,以用于后续像素点进行GOLOMB-RICE编码时K值的选取。

2 压缩系统硬件设计

设计采用 4 级流水线结构,系统只有一个主时钟CLK作为工作时钟。硬件实现包括控制单元、上下文模型选取单元、预测单元、熵编码单元和并串转换单元,硬件结构框图如图 4。

控制单元负责产生控制信号以协调各电路模块的工作顺序;上下文模型选取单元将像素值输入存储器进行存储,产生当前像素、相邻像素和上下文预测值Δ;预测单元根据不同的上下文模型求出像素残余值;编码单元对像素残余值进行修正的二元编码或GOLOMB-RICE编码;并串转换单元负责将编码结果转换为码流进行输出。

图5所示为各个电路子模块的接口定义及连线图。其中上下文产生模块和预测模块功能具有连续性,用一个模块表示,像素值以光栅扫描的顺序逐行进行读入,需要一个行存储器对像素值进行存储,每完成对一个像素点的编码操作之后,将存储器中该处的像素值更新为当前行当前列的像素值,本方案处理的图像大小为512*512,因此只需要一个512*8比特的存储器。修正二元编码和GOLOMB-RICE编码模块算法相对复杂一些,为了加快系统的时钟频率,将算法中的计算步骤进行拆分细化。GOLOMB-RICE编码模块需要进行参数K的选取,若K的可能值有4个,则还需要256*8*4比特大小的存储器作为累加表。最后,由于编码后的码值是变长的,为了满足输出端口的要求,要对编码结果进行并串转换操作,输出端以码流的形式进行输出。

压缩系统已集成在XILINX VIRTEX-5 FPGA上,并利用开发板XUPV5_LX110T进行了验证,当工作频率为20MHZ时, 吞吐率可达45f/s,所需存储空间仅为13.1Kbits,每帧的功耗仅为13.67毫瓦。经过若干经典图像测试后发现此压缩系统的平均压缩比为2.2,和主流的无损图像压缩算法(如JPEG-LS)相当,但压缩效率提升约80%左右。

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)