Xilinx FPGA入门连载23:PLL实例之功能简介

时间:11-10

来源:互联网

点击:

Xilinx FPGA入门连载23:PLL实例之功能简介

特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1jGjAhEm

PLL(Phase Locked Loop):为锁相回路或锁相环,用来统一整合时脉讯号,使内存能正确的存取资料。PLL用于振荡器中的反馈技术。许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。

而我们在这里所说的PLL,没有上面一段定义那么晦涩难懂,大家记住PLL一个最主要的功能,即能够对输入的基准时钟信号进行一定范围内的分频或者倍频,从而产生多个输出时钟信号供芯片内部的各个功能模块使用。

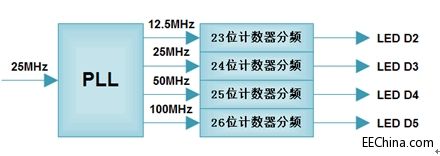

2 功能简介如图所示,本实例将用到FPGA内部的PLL资源,输入FPGA引脚上的25MHz时钟,配置PLL使其输出4路分别为12.5MHz、25MHz、50MHz和100MHz的时钟信号,这4路时钟信号又分别驱动4个不同位宽的计数器不停的计数工作,这些计数器的最高位最终输出用于控制4个不同的LED亮灭。由于这4个时钟频率都有一定的倍数关系,所以我们也很容易通过调整合理的计数器位宽,达到4个LED闪烁一致的控制。

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- 迄今为止最牛的ASIC验证平台(05-22)

- 验证FPGA设计:模拟,仿真,还是碰运气?(08-04)