Xilinx FPGA入门连载9:Verilog语法检查

时间:09-23

来源:互联网

点击:

Xilinx FPGA入门连载9:Verilog语法检查

特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1jGjAhEm

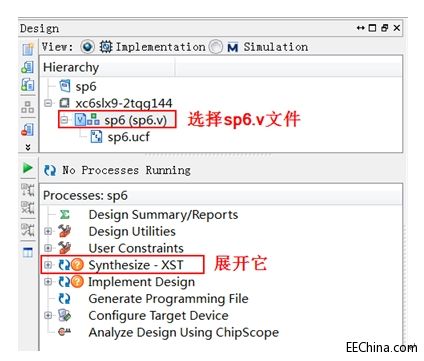

继续上一个lesson,我们已经创建并且编辑好Verilog源码文件。现在我们要到ISE中对这个源码进行语法检查。如图所示,在“Hierarchy”下,我们需要先选中sp6.v这个源代码文件。接着在“Processes”中单击“Synthesize - XST”前面的“+”号,展开综合选项。

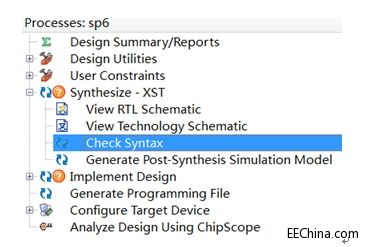

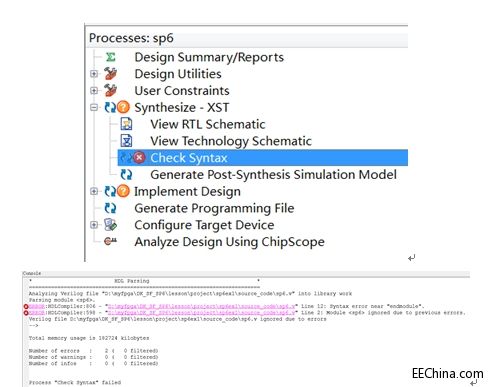

如图所示,展开“Synthesize- XST”后,我们看到了4个选项,双击“Check Syntax”这个项目,即“语法检查”功能。

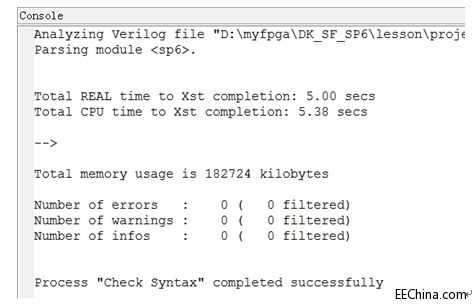

数秒后,我们可以看到“CheckSyntax”选项的前面出现了绿色的勾号,说明语法检查完成,并且通过。

与此同时,在ISE最下方的“Console”窗口中,打印了语法检查结果的报告。如图所示,这里看到语法检查没有发现任何的errors和warnings。

当然了,如果有语法错误时,会是什么情况呢?大家不妨自己动手试试,随便将源代码中的某个“;”去掉,在重新进行“Check Syntax”后,就可以出现如下的提示和报告。

语法检查有一点非常好,就是在ERROR中会明确定位的具体出错的位置,即某一个LINE附近(注意是附近,不一定就能准确定位到错误的那一行,可能是它的上下行)有错误,大家可以根据这个提示查找错误。另外必须提醒注意的是,并不是有几个ERROR就表示有几个实际的ERROR,可能多个ERROR对应的是一个实际的ERROR。

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- 迄今为止最牛的ASIC验证平台(05-22)

- 验证FPGA设计:模拟,仿真,还是碰运气?(08-04)