FPGA实战演练逻辑篇37:可综合的语法子集2

可综合的语法子集2

本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》

配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt

(1) 参数定义:parameter。(特权同学,版权所有)

Parameter用于申明一些常量,主要是便于模块的移植或升级时的修改。(特权同学,版权所有)

一个基本的module,通常一定包括module…endmodule语法和任意两种端口申明(通常我们所设计的模块一定是有输入和输出的),parameter则不一定,但是对于一个可读性强的代码来说也是不可少的。这样一个基本的module如下:

module <模块命名>(<端口命名1>, <端口命名2>, ...);

// 输入端口申明

input <端口命名1>;

input wire <端口命名2>;

input [<最高位>:<最低位>]<端口命名3>;

...

// 输出端口申明

output <端口命名4>;

output [<最高位>:<最低位>]<端口命名5>;

output reg [<最高位>:<最低位>]<端口命名6>;

...

// 双向(输入输出)端口申明

inout <端口命名7>;

inout [<最高位>:<最低位>]<端口命名8>;

...

// 参数定义

parameter <参数命名1> = <默认值1>;

parameter [<最高位>:<最低位>]<参数命名2> = <默认值2>;

...

// 具体功能逻辑代码

...

endmodule

注:“//”后的内容为注释。(特权同学,版权所有)

(2) 信号类型:wire,reg等。(特权同学,版权所有)

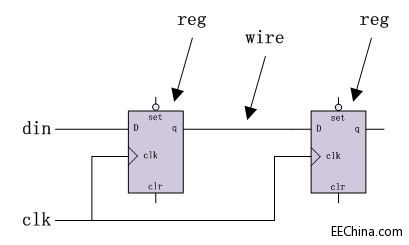

如图5.1所示,在这个简单的电路中,分别定义两个寄存器(reg)锁存当前的输入din。每个时钟clk上升沿到来时,reg都会锁存到最新的输入数据,而wire就是这两个reg之间直接的连线。(特权同学,版权所有)

作为input或inout的信号端口只能是wire型,而output则可以是wire也可以是reg。需要特别说明的是,虽然在代码中我们可以定义信号为wire或reg类型,但是实际的电路实现是否和我们预先的一致还要看综合工具的表现。例如reg定义的信号通常会被综合为一个寄存器(rigister),但这有一个前提,就是这个reg信号必须是在某个由特定信号边沿敏感触发的always语句中被赋值。(特权同学,版权所有)

图5.1 reg和wire示例图

Wire和reg的一些常见用法示例如下:

// 定义一个wire信号

wire <wire变量名>;

// 给一个定义的wire信号直接连接赋值

// 该定义等同于分别定义一个wire信号和使用assign语句进行赋值

wire <wire变量名> =<常量或变量赋值>;

// 定义一个多bit的wire信号

wire [<最高位>:<最低位>] <wire变量名>;

// 定义一个reg信号

reg <reg变量名>;

// 定义一个赋初值的reg信号

reg <reg变量名> =<初始值>;

// 定义一个多bit的reg信号

reg [<最高位>:<最低位>] <reg变量名>;

// 定义一个赋初值的多bit的reg信号

reg [<最高位>:<最低位>] <reg变量名> = <初始值>;

// 定义一个二维的多bit的reg信号

reg [<最高位>:<最低位>] <reg变量名> [<最高位>:<最低位>];

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)