FPGA实战演练逻辑篇33:实时时钟芯片电路设计

时间:06-05

来源:互联网

点击:

实时时钟芯片电路设计

本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》

配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt

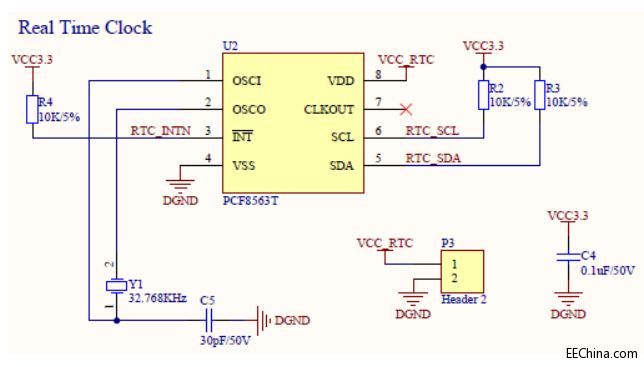

如图3.76所示,U2是一颗实时时钟(RTC)芯片,该芯片需要外部供32.768KHz的时钟晶体,这个晶体的振荡需要借助一颗30Pf(8pF)的电容。该芯片和FPGA之间通过I2C总线接口进行数据传输。该芯片的供电要借助外部连接的一颗纽扣电池。(特权同学,版权所有)

图3.76 实时时钟接口电路

U2的各个引脚定义如表3.13所示。(特权同学,版权所有)

表3.13 实时时钟芯片的引脚定义

| 引脚 | 信号 | 功能 |

1 | OSCI | 32.768KHz晶体输入引脚。 |

2 | OSCO | 32.768KHz晶体输出引脚。 |

3 | INT# | RTC芯片中断产生引脚。 |

4 | DGND | 电源地。 |

5 | SDA | 用于读写寄存器的I2C总线数据信号。 |

6 | SCL | 用于读写寄存器的I2C总线时钟信号。 |

7 | CLKOUT | 时钟输出引脚,本实例不使用,直接悬空。 |

8 | VDD | 芯片电源输入,连接到3V的纽扣电池供电。 |

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- FPGA按键模式的研究与设计(03-24)

- 周立功:如何兼顾学习ARM与FPGA(05-23)