FPGA入门:表面现象揭秘——逻辑关系

FPGA入门:表面现象揭秘——逻辑关系

本文节选自特权同学的图书《FPGA/CPLD边练边学——快速入门Verilog/VHDL》

书中代码请访问网盘:http://pan.baidu.com/s/1bndF0bt

神奇的0和1,缘何能够如此的变化多端?从某种意义上看,无非就是数字本身固有的各种各样的逻辑关系在使然。在今天的数字系统中,虽然可能整个系统的不同芯片或相同芯片的不同模块之间供给电压不尽相同,有5V/3.3V/2.5V/1.8V/1.2V等等,但是从基本原理上看,无论用什么电压值代表1(通常都一致的用0V表示0),其内部逻辑运算原理都是一致的。

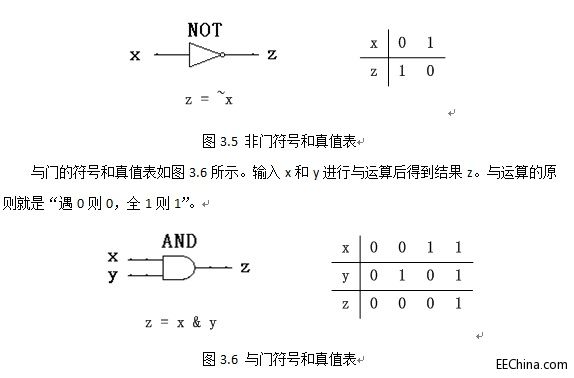

0和1,他们的最基本逻辑运算是通过非门、与门和或门来实现的。非门的符号和真值表如图3.5所示。输入x经过非门后,输出z为x的取值反向,如输入x=0则z=1,反之,输入x=1则z=0。

图3.6 与门符号和真值表

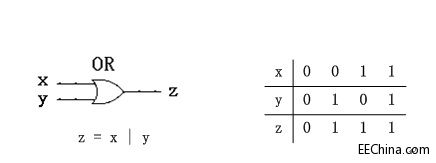

或门的符号和真值表如图3.7所示。输入x和y进行或运算后得到结果z。或运算的原则就是“遇1则1,全0则0”。

图3.7 或门符号和真值表

在与、或、非这三种最基本的逻辑门基础上进行一些扩展,就产生了一些常见的逻辑门如与非门、或非门、异或门、同或门,其符号和真值表分别如图3.8、图3.9、图3.10和图3.11所示。

图3.11 同或门符号和真值表

有了这些基本的门电路,可能有些人还是不理解,到底这些门电路能够干什么,只是做做简单的逻辑关系处理?非也,数字电路中的逻辑门其实就如同数学运算中的1+1=2和2-1=1这样简单却又非常基础的关系。数字电路的逻辑门说白了也是为数学运算服务的,人类运算的基础——加、减、乘、除都可以用逻辑门来完成,更高级一些的运算如开方、求根号等,一样可以通过一些巧妙的逻辑门处理算法解决。人类不是有一套十进制的运算方式了,那又为什么一定要通过逻辑门以二级制的方式来完成这类运算呢?究其根本原因,是因为二进制的处理机制是数字电路(或者更大一点说,也是计算机技术)的基础,而基本的逻辑门运算又非常适合于二进制的运算。再往后,如果读者有机会更深入到电子或计算机相关的应用中,回头再望望今天所说的这些基本逻辑门电路,一定会惊叹那些计算机前辈们的智慧。可不是,话说能够用最简单的东西实现最复杂的事物那才是人类创造的最高水平。

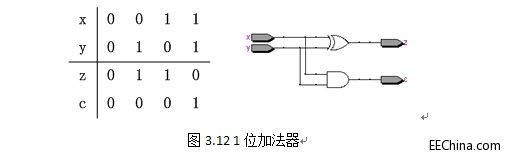

下面列举一个最简单的1位加法器的例子,如图3.12所示,x和y相加,其结果为z,进位为c。我们观察其真值表发现:z = x^y,c = x&y。果然,1位加法非常轻易的用两个逻辑门电路实现了。

图3.12 1位加法器

若是再深入,2位、3位甚至更多位的加法运算,对于每个位的结果和进位,都可以仿照1位加法器的方式来实现。由此可见,逻辑门还真是那么回事。

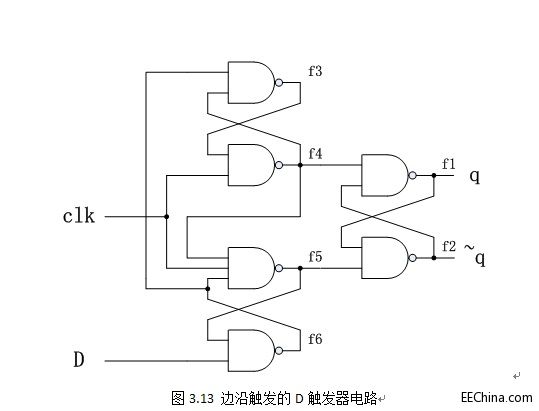

接下来,我们要用这些基本的逻辑门搭个复杂点的电路。这个电路如图3.13所示,这是边沿触发的D触发器电路。该触发器的功能是实现时钟信号clk上升沿(由0变化到1)时将输入信号D的值锁存到输出信号q。

图3.13 边沿触发的D触发器电路

该D触发器的真值表如表3.1所示。由此表不难看出,这个D触发器实现了clk信号的上升沿锁存当前输入D信号值到输出信号q或~q的功能,而当clk信号为0或者保持高电平期间,D信号的取值变化不会影响当前的输出q和~q。

表3.1 D触发器真值表

| D | clk | f3 | f4 | f5 | f6 | f1 | f2 | q | ~q |

0 | 0 | 0 | 1 | 1 | 1 | - | - | - | - |

1 | 0 | 1 | 1 | 1 | 0 | - | - | - | - |

↓ | 0 | 0 | 1 | 1 | 1 | - | - | - | - |

↑ | 0 | 1 | 1 | 1 | 0 | - | - | - | - |

0 | ↑ | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

1 | ↑ | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 |

↑ | 1 | 0 | 1 | 0 | 1 | - | - | - | - |

↓ | 1 | 1 | 0 | 1 | 1 | - | - | - | - |

0 | ↓ | 0 | 1 | 1 | 1 | - | - | - | - |

1 | ↓ | 1 | 1 | 1 | 0 | - | - | - | - |

由此可见,D触发器可用于存储比特信号,当D输入为0时,在时钟clk的上升沿,q输出也为0;当D输入为1时,在时钟clk的上升沿,q输出也为1;在其他的时刻,q输出保持不变。在实际电路中,时钟信号clk源源不断的有标准的方波输入,每个时钟信号clk的上升沿都会使得D触发器的输入D值被锁存到输出q值中。其实这个D触发器就是我们最基本的寄存器的雏形了,在时序电路中,寄存器和时钟是最基本的要素。

如图3.14所示,这是一个带有异步置位和复位功能的D触发器。所谓置位,即set信号有效时(即为1时),该电路无论时钟clk和输入D值的状态如何,输出q一定是1;同理,所谓复位,即指clr信号有效时(即为1时),该电路无

FPGA CPLD Verilog VHDL 电压 电路 电子 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)