零基础学FPGA(十八)testbench很重要,前仿真全过程笔记(下篇)

时间:01-20

来源:互联网

点击:

作者:小墨同学

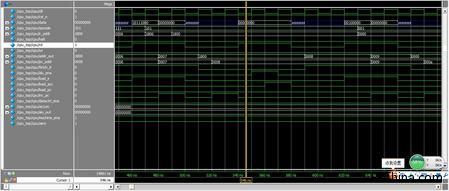

进入波形仿真后点击运行按钮即可出波形,下面我们来验证我们的cpu代码是否正确

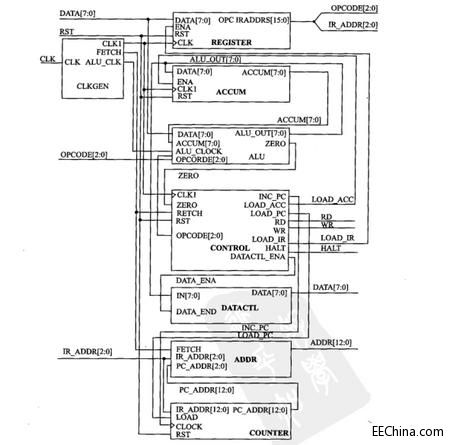

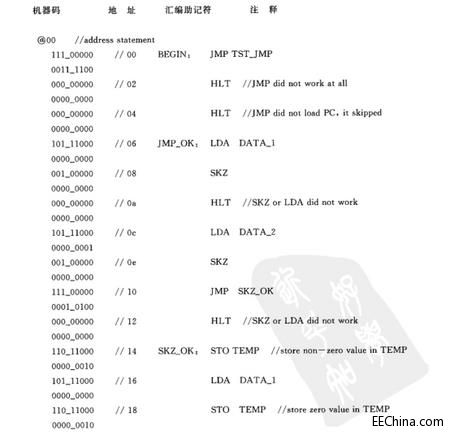

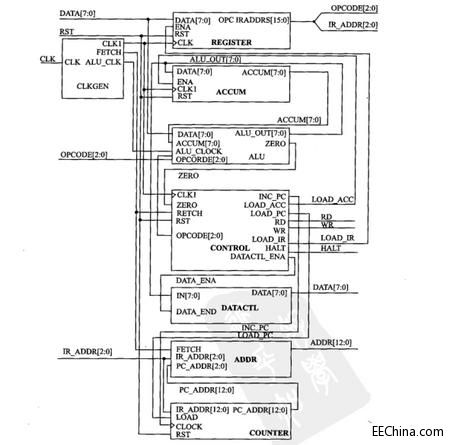

大家先看两个图,等会小墨同学会结合这两个图给大家细细讲解仿真过程

我们先来看第一个过程

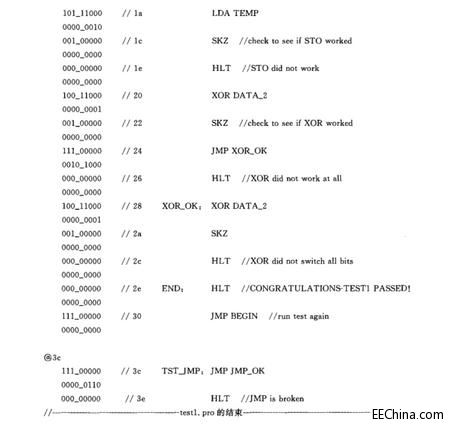

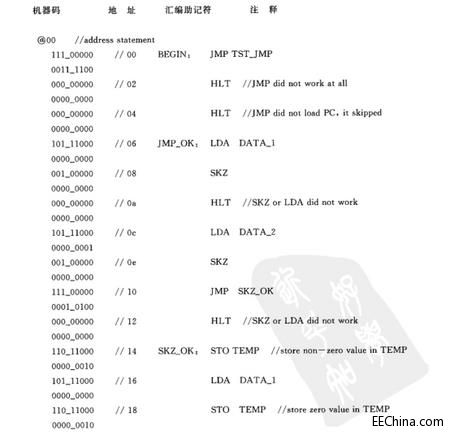

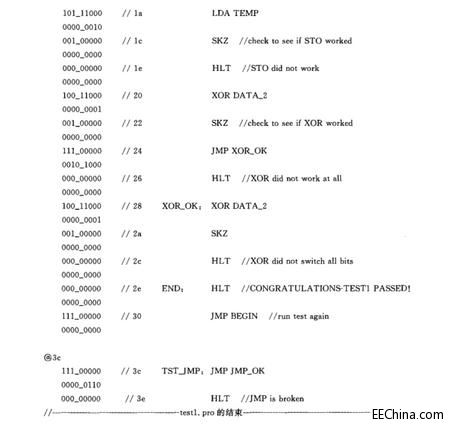

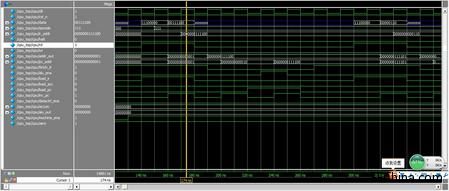

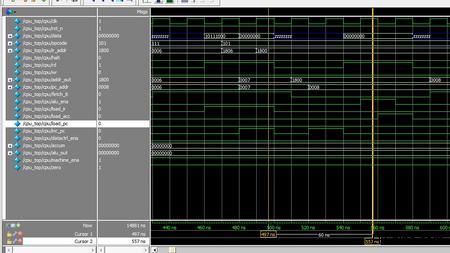

上电后,cpu先从ROM中读回两个周期的数据,是从ROM的0地址开始的,再对比我们之前定义好的ROM,数据读取正确,读回的数据的前三位是111,即指令码JMP,后13位003c为地址码,JMP指令是将读回的数据作为新的地址码来读取相应地址的数据。那么,下一步,cpu应该是从ROM的003c地址处读数据才对,再看一下波形

对比波形后可知,cpu正好是从003c处读取数据,读到的数据指令码位111即JMP,地址码位0006,再到ROM的0006地址处看

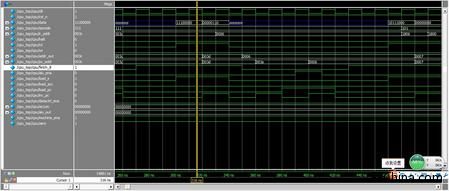

这次读回的指令码位101,即LDA,也就是说将后13位地址码对应的RAM中的数据读回,送到累加器中,想一下,这时的RAM应该是打开的,而且双向输入输出口的数据总线上应该是来自RAM的8位数据,由于ROM0006地址处的地址码为1800是13位的,而RAM的地址是9位的,因此实际上我们从RAM中读回的数据是从RAM的0地址读回的,即我们之前给RAM写好的0000_0000,再看一下波形

正如我们所想的一样,数据总线上是0000_0000,RAM是打开的,地址为1800

就这样,读者可以自己再试一下,看看我们的cpu是不是按照我们之前给他的程序运行的,在这里我就不再给大家一一介绍了

虽然波形仿真很直观,但是看久了就会令人眼花缭乱,尤其是数据很多的时候,我们只能看其中一部分,不能讲所有数据看完整,这时候我们单单是用波形来仿真就远远不够了,下面介绍用系统任务仿真的过程

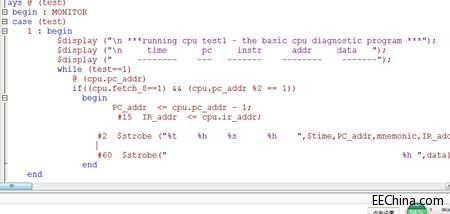

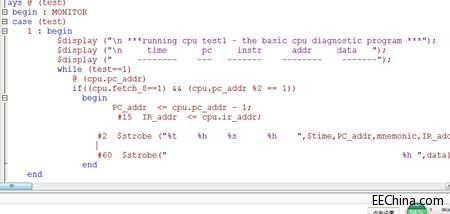

再回到我们的代码,还记得小墨同学注释掉了一些代码吧,我们把那些代码给加上

我以其中一个过程为例

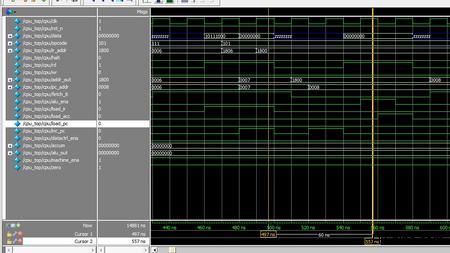

假设读回的指令码位101,即LDA,如果我在fentch_8的高电平期间且在cpu输出地址为奇数的时候记录一下此时的时间、指令、地址、目的地址、数据的话就可以不用看波形,让电脑来帮助我们来分析了,因此作如下处理

这里我延时60ns,是因为第一次记录的时候数据总线上还没有数据,只有延时一会才会有数据,即上面那张波形图右边那根黄色的线处记录一下数据,并将其显示。我们也可以加上一下标注,来帮助我们观察

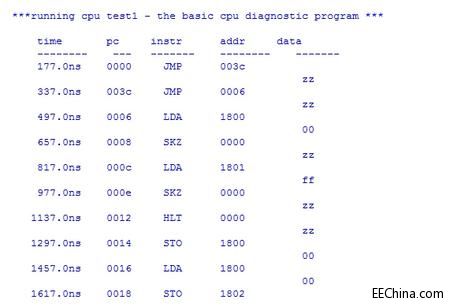

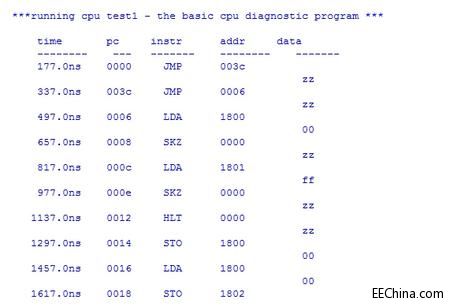

这样我们再来仿真的时候就不用看波形了,直接打开transcript一栏观察记录即可

这样便可以为我们省下大量的仿真时间

这里小墨同学只做一个事例,其实有很多细节还需要各位读者自己挖掘,小墨同学在做这个实验的时候也遇到过不少问题,但是问题总是要解决的,希望各位读者不要老借助于教程,遇到问题需要自己解决,自己考虑一下应该怎么修改,这样学到的知识才是最牢固的。

这里小墨同学只做第一个测试,第二第三个测试留给读者自己完成,我已上传过代码,希望广大读者多提意见,大家共同进步

纯手打~谢谢各位大神支持~

此外,以后小墨同学的文章将北京至芯科技官方技术论坛更新,至芯科技的官方技术论坛也有很多的资料供大家下载,里面也有小墨的专题板块,希望广大网友和爱好者的大力支持~

http://www.fpgaw.com/

小墨同学专版网址

http://www.fpgaw.com/thread-78527-1-1.html

下面是至芯科技官方网站,夏宇闻教授和那里的老师都超好的~有意愿接受FPGA培训的可以找工作人员咨询

http://www.zxopen.com/

以后小墨同学的教程会跟这款开发板配套,想跟小墨同学一起学习,一起进步的的可以考虑一下购买一块开发板,毕竟学习要舍得投资嘛,下面是开发板淘宝链接

http://item.taobao.com/item.htm? ... ;abbucket=13#detail

进入波形仿真后点击运行按钮即可出波形,下面我们来验证我们的cpu代码是否正确

大家先看两个图,等会小墨同学会结合这两个图给大家细细讲解仿真过程

我们先来看第一个过程

上电后,cpu先从ROM中读回两个周期的数据,是从ROM的0地址开始的,再对比我们之前定义好的ROM,数据读取正确,读回的数据的前三位是111,即指令码JMP,后13位003c为地址码,JMP指令是将读回的数据作为新的地址码来读取相应地址的数据。那么,下一步,cpu应该是从ROM的003c地址处读数据才对,再看一下波形

对比波形后可知,cpu正好是从003c处读取数据,读到的数据指令码位111即JMP,地址码位0006,再到ROM的0006地址处看

这次读回的指令码位101,即LDA,也就是说将后13位地址码对应的RAM中的数据读回,送到累加器中,想一下,这时的RAM应该是打开的,而且双向输入输出口的数据总线上应该是来自RAM的8位数据,由于ROM0006地址处的地址码为1800是13位的,而RAM的地址是9位的,因此实际上我们从RAM中读回的数据是从RAM的0地址读回的,即我们之前给RAM写好的0000_0000,再看一下波形

正如我们所想的一样,数据总线上是0000_0000,RAM是打开的,地址为1800

就这样,读者可以自己再试一下,看看我们的cpu是不是按照我们之前给他的程序运行的,在这里我就不再给大家一一介绍了

虽然波形仿真很直观,但是看久了就会令人眼花缭乱,尤其是数据很多的时候,我们只能看其中一部分,不能讲所有数据看完整,这时候我们单单是用波形来仿真就远远不够了,下面介绍用系统任务仿真的过程

再回到我们的代码,还记得小墨同学注释掉了一些代码吧,我们把那些代码给加上

我以其中一个过程为例

假设读回的指令码位101,即LDA,如果我在fentch_8的高电平期间且在cpu输出地址为奇数的时候记录一下此时的时间、指令、地址、目的地址、数据的话就可以不用看波形,让电脑来帮助我们来分析了,因此作如下处理

这里我延时60ns,是因为第一次记录的时候数据总线上还没有数据,只有延时一会才会有数据,即上面那张波形图右边那根黄色的线处记录一下数据,并将其显示。我们也可以加上一下标注,来帮助我们观察

这样我们再来仿真的时候就不用看波形了,直接打开transcript一栏观察记录即可

这样便可以为我们省下大量的仿真时间

这里小墨同学只做一个事例,其实有很多细节还需要各位读者自己挖掘,小墨同学在做这个实验的时候也遇到过不少问题,但是问题总是要解决的,希望各位读者不要老借助于教程,遇到问题需要自己解决,自己考虑一下应该怎么修改,这样学到的知识才是最牢固的。

这里小墨同学只做第一个测试,第二第三个测试留给读者自己完成,我已上传过代码,希望广大读者多提意见,大家共同进步

纯手打~谢谢各位大神支持~

此外,以后小墨同学的文章将北京至芯科技官方技术论坛更新,至芯科技的官方技术论坛也有很多的资料供大家下载,里面也有小墨的专题板块,希望广大网友和爱好者的大力支持~

http://www.fpgaw.com/

小墨同学专版网址

http://www.fpgaw.com/thread-78527-1-1.html

下面是至芯科技官方网站,夏宇闻教授和那里的老师都超好的~有意愿接受FPGA培训的可以找工作人员咨询

http://www.zxopen.com/

以后小墨同学的教程会跟这款开发板配套,想跟小墨同学一起学习,一起进步的的可以考虑一下购买一块开发板,毕竟学习要舍得投资嘛,下面是开发板淘宝链接

http://item.taobao.com/item.htm? ... ;abbucket=13#detail

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- FPGA按键模式的研究与设计(03-24)

- 验证FPGA设计:模拟,仿真,还是碰运气?(08-04)